# FPGA Design with VHDL

Justus-Liebig-Universität Gießen, II. Physikalisches Institut

> <u>Ming Liu</u> Dr. Sören Lange Prof. Dr. Wolfgang Kühn

ming.liu@physik.uni-giessen.de

## Lecture 2

- FPGA Development Flow

- VHDL Basics

- Concurrent Design

- Sequential Design

- Coding Style Issues

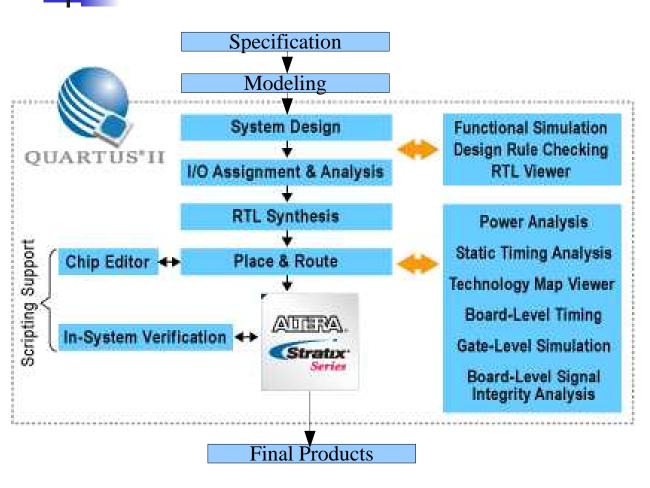

### **FPGA Development Flow**

- Specification & modeling (algorithm investigation with high-level languages)

- System design (coding)

- Hardware description (HDL)

- Simulation (functional simulation or presimulation)

- Constraints (timing, location assignments, ...)

- Synthesis & Implementation (timing simulation or postsimulation)

- System verification & final products

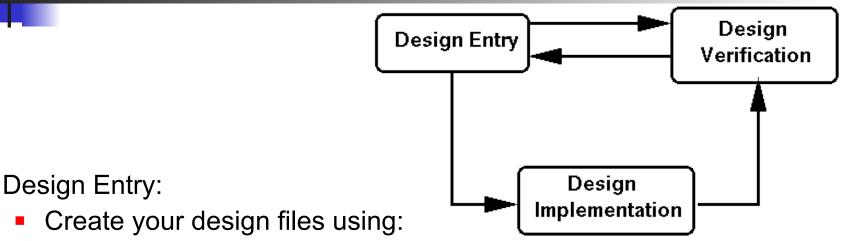

## Simplified Development Flow

- hardware description (Verilog, VHDL)

- Design "implementation" on FPGA:

- Synthesis, map, place, and route to create bit-stream file

- Divide into CLB-sized pieces, place into blocks, route to blocks

- Design verification:

- Use Simulator to check functionality

- check max clock frequency

- Load into FPGA device (cable connects PC to board)

- check operation at full speed in real environment.

- C or SystemC compilers for modeling (for complicated algorithms, can be neglected for simple designs)

- Editors for coding: Emacs, etc..

- Simulation software: Modelsim

- Synthesis & Implementation software: Xilinx ISE

- Other useful tools in the Xilinx software package, such as EDK, Chipscope, FPGA editor, ...

## **VHDL Basics**

- <u>VHSIC Hardware Description Language</u> (<u>Very High Speed Integrated Circuit</u>)

- Synthesizable (for implementation) & unsynthesizable subset (for simulation)

- Detailed syntax:

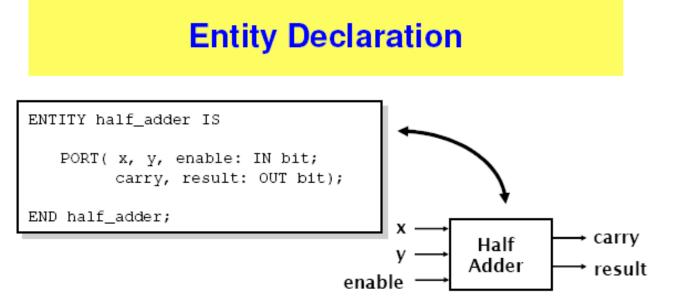

- An entity declaration describes the interface of the component

- PORT clause indicates input and output ports

- An entity can be though of as a symbol for a component

### **VHDL Basics**

### **Port Declaration**

ENTITY test IS PORT( name : mode data\_type); END test;

### **Architecture Declaration**

• PORT declaration establishes the interface of the object to the outside world

- Three parts

- Name

- Mode (in, out)

- Data type (std\_logic,

std\_logic\_vector, ...)

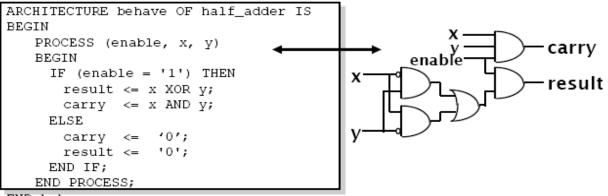

• Architecture declarations describe the operation of the component

Many architectures may exist for one entity, but only one may be active at a time

An architecture is similar to a schematic of the component

END behave;

## **VHDL Basics**

### Generics

- Generics allow the component to be customized upon instantiation

- · Generics pass information from the entity to the architecture

- Common uses of generics

- Customize timing

- Alter range of subtypes

- Change size of arrays

### Example 2:

The GENERIC MAP is similar to the PORT MAP in that it maps specific values to generics declared in the component

### Example 1:

```

entity user_logic is

generic (DATA_WIDTH : integer := 16);

port(

data_in : in std_logic_vector(DATA_WIDTH - 1 downto 0);

.....

);

end entity user_logic;

architecture arc of user_logic is

signal counter : std_logic_vector(DATA_WIDTH - 1 downto 0);

.....

end arc;

```

```

PACKAGE my_stuff IS

COMPONENT and_gate

GENERIC ( tplh, tphl : time);

PORT ( in1, in2 : IN BIT; out1 : OUT BIT);

END COMPONENT;

END my_stuff;

USE Work.my_stuff.ALL;

ARCHITECTURE test OF test_entity

SIGNAL S1, S2, S3 : BIT;

BEGIN

Gate1 : my_stuff.and_gate

GENERIC MAP (2 ns, 3 ns)

PORT MAP (S1, S2, S3);

END test;

```

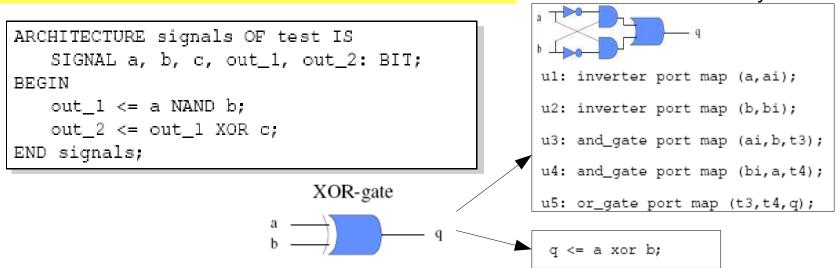

## VHDL Basics – Concurrent Design

### **Signal Declaration**

```

SIGNAL signal_name : type_name [:=value];

SIGNAL brdy : BIT;

SIGNAL output : INTEGER := 2;

```

### **Signal Assignment**

• Signals are used for communication between components

• Signals can be seen as real, physical signals

• Some delay must be incurred in a signal assignment

• Signals can be assigned either in the behavioral style or in the structural style

## VHDL Basics – Concurrent Design

#### **IF- vs CASE-statement Syntax**

FOR- vs WHILE-statement Syntax

if (a='1') then

q <= '1';

elsif (b='1') then

q <= '1';

else

q <='0';</pre>

end if;

case (a&b) 1s

when "00" =>

q <= '0';

when others =>

q <= '1';

end case;</pre>

#### WAIT-statement Syntax

- · The wait statement causes the suspension of a process statement or a procedure

- wait [sensitivity\_clause] [condition\_clause] [timeout\_clause ] ;

- sensitivity\_clause ::= on signal\_name { , signal\_name }

wait on CLOCK;

condition\_clause ::= until boolean\_expression

wait until Clock = `1';

- timeout\_clause ::= for time\_expression

wait for 150 ns;

for 1 in 0 to 9 loop

q(1) <= a(1) and b(1);

end loop;

For is considered to be a combinational circuit by some synthesis-tools. Thus, it cannot have a wait statement to be synthesised.

1:=0;

while (i<9) loop

q <= a(i) and b(i);

WAIT ON clk UNTIL clk='1';</pre>

While is considered to be an FSM by some synthesis-tools. Thus, it needs a wait statement to be synthesised

end loop;

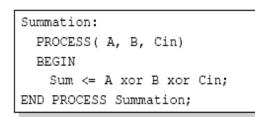

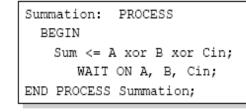

### VHDL Basics – Concurrent Design

#### Sensitivity-lists vs Wait-on-statement

=

If you put a sensitivity list in a process, you can't have a wait statement!

If you put a wait statement in a process, you can't have a sensitivity list!

#### **Concurrent Process Equivalents**

All concurrent statements correspond to a process equivalent

U0:q <= a xor b after 5 ns;

is a short hand notation for

U0:process

begin

q <= a xor b after 5 ns;

wait on a,b;

end process;

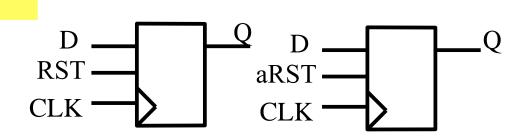

## VHDL Basics – Sequential Design

#### Flip-flop

process(clk) -- synthesis might complain that d is not listed

#### begin

if (clk='1') and clk'event then

q<=d;

end if;

end process;

#### **D-flipflop with synchronous reset**

process(clk) -- synthesis might complain that neither d nor -- reset is listed

#### begin

if (clk='1') and clk'event then if (reset='1') then q<='0'; else q<= D; end if; end if;

#### end process;

#### **Asynchronous reset**

process(clk,reset) -- synthesis might complain that d is not -- listed

#### begin

```

if (reset='1') then

q<='0';

```

elsif (clk='1') and clk'event then

q<= D;

end if;

end process;

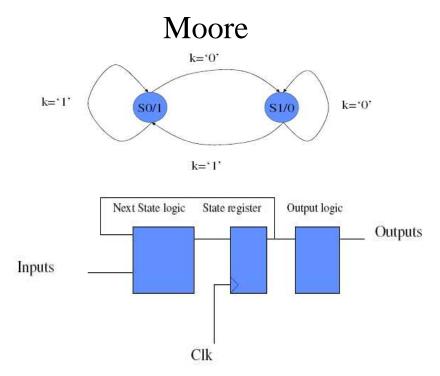

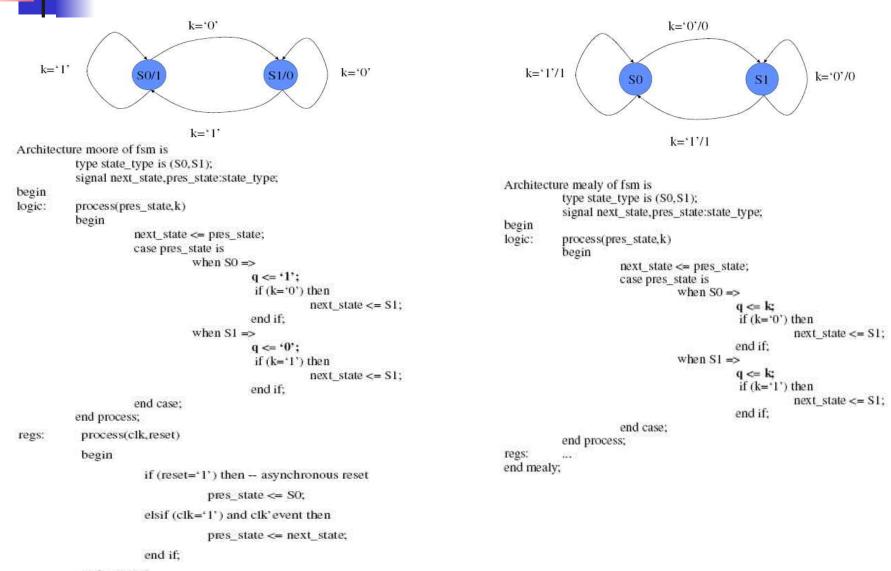

- Finite State Machine (FSM)

- Mealy Machine & Moore Machine

$\begin{array}{c} \textbf{Mealy} \\ \textbf{k}=`1'/1 & \textbf{k}=`0'/0 \\ \textbf{k}=`1'/1 & \textbf{k}=`0'/0 \\ \textbf{k}=`1'/1 & \textbf{current state} \\ \hline \textbf{Next State logic State register Output logic Outputs} \\ \textbf{Inputs } & \textbf{next state Clk} \end{array}$

Moore machine: The output has only to do with the current state.

Mealy machine: The output has not only to do with the current state, but also with the input.

### VHDL Basics – Sequential Design

end process;

end moore;

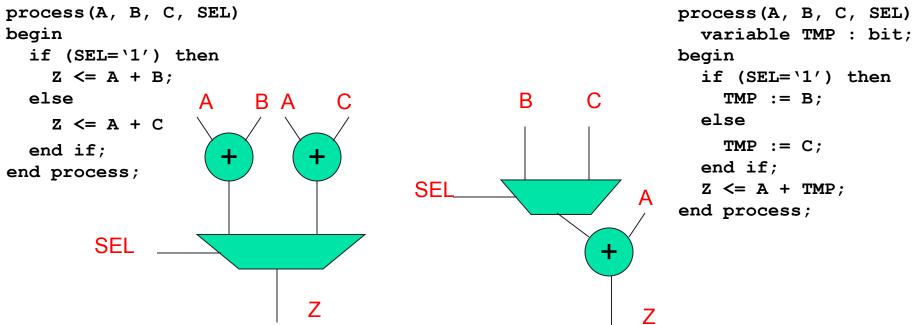

### **Coding Style Issues**

- Structure of initially generated hardware is determined by the VHDL code itself

- Synthesis optimizes that initially generated hardware, but cannot do dramatic changes

- Therefore, coding style matters!

### Coding Style Issues

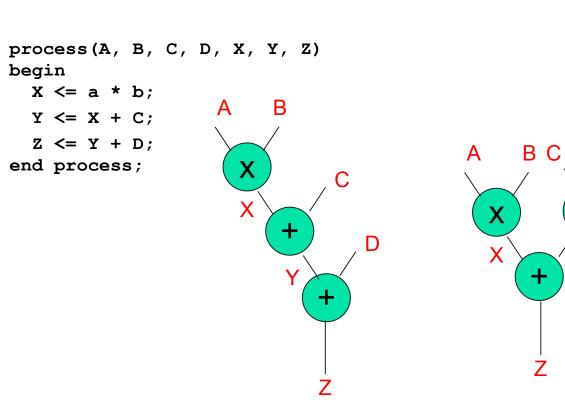

process(A, B, C, D, X, Y, Z)

begin

X <= a \* b;

Y <= C + D;

Z <= X + Y;

end process;</pre>

CP = Mul + Add + Add

CP = Mul + Add

+

Some more words on comparing VHDL with C VHDL C sw description language hw description language sequential execution parallel architecture single core multiple processing elements machine codes on CPUs logic elements on FPGAs high clk frequency (GHz) low clk frequency (MHz) limited parallelism massive parallelism

So don't use the sw programming concepts in VHDL. A good VHDL coding style is to Think In Hardware!!!

- The VHDL Golden Reference Guide

- Actel HDL Coding Style Guide

- Other VHDL books