# System-on-an-FPGA Design for Real-time Particle Track Recognition and Reconstruction in Physics Experiments

**Ming Liu<sup>†‡</sup>**, Wolfgang Kuehn<sup>†</sup>, Zhonghai Lu<sup>‡</sup>, Axel Jantsch<sup>‡</sup>

II. Experimental Physics Institute, Justus-Liebig-University in Giessen, Germany

Dept. of Electronic, Computer and Software Systems, Royal Institute of Technology, Stockholm, Sweden

## Outline

- Background & algorithm description

- Tracking Processing Unit (TPU) design on FPGA

- Experimental results

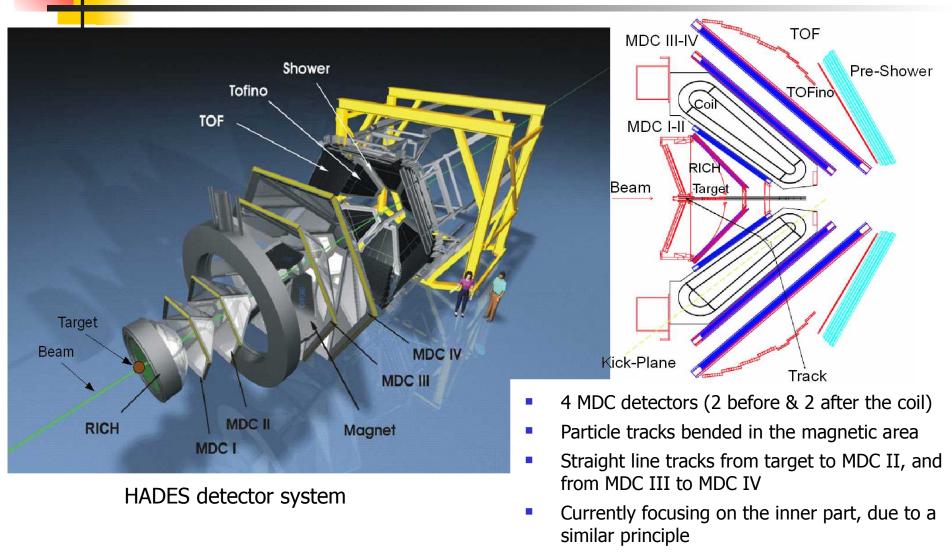

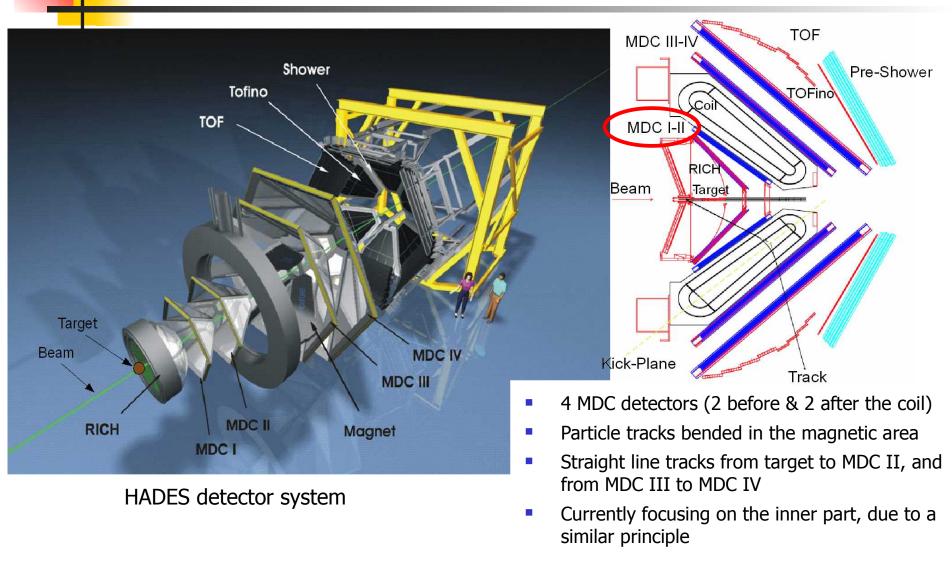

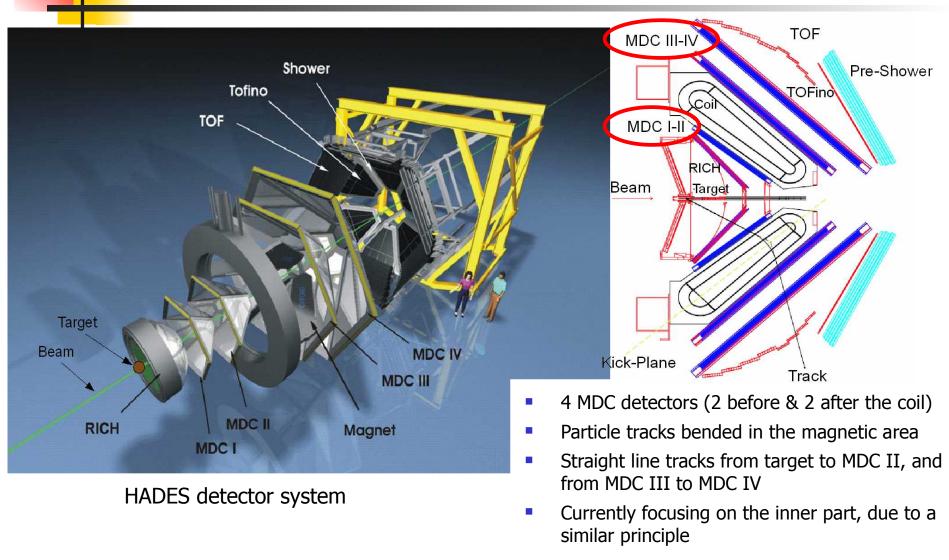

### **Detector System for Particle Collisions**

Sep. 5, 2008

### **Detector System for Particle Collisions**

Sep. 5, 2008

### **Detector System for Particle Collisions**

Sep. 5, 2008

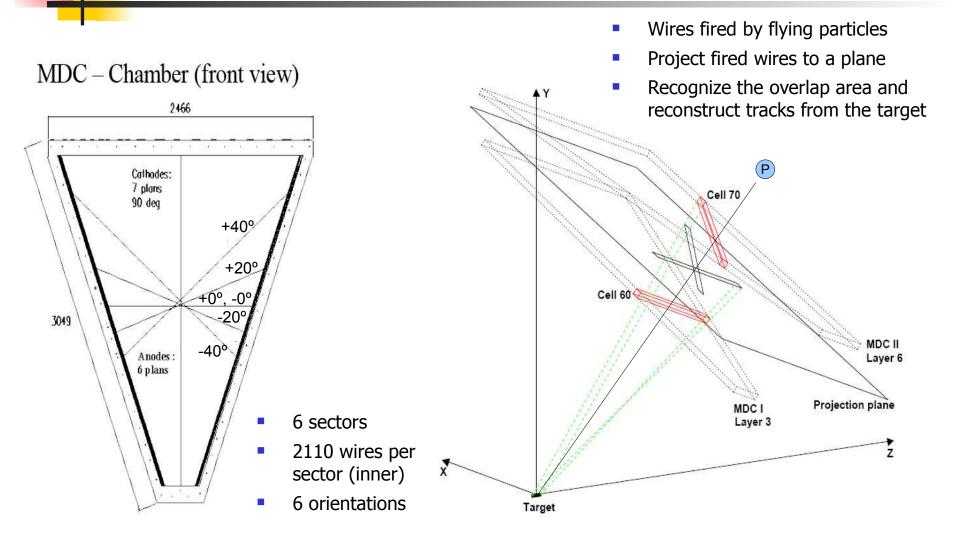

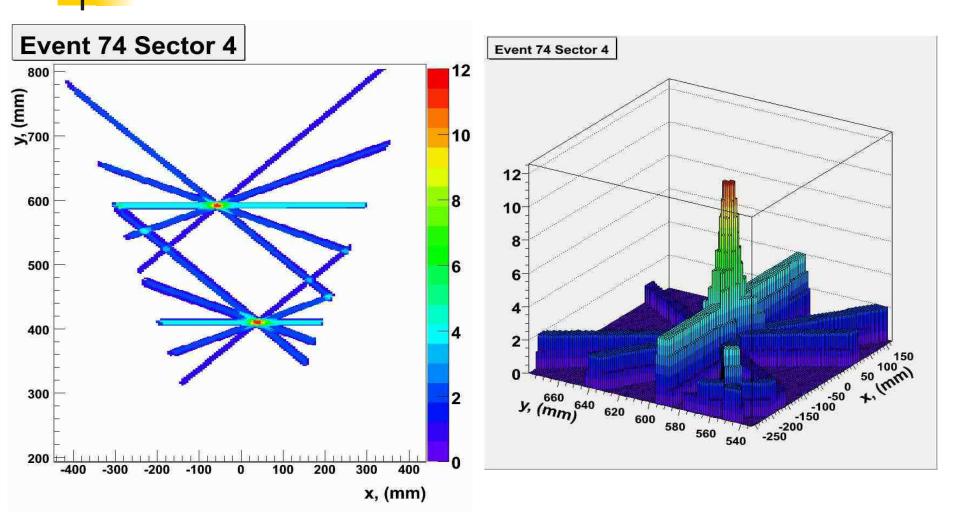

### Principle of the Tracking Algorithm

### Principle of the Tracking Algorithm

Sep. 5, 2008

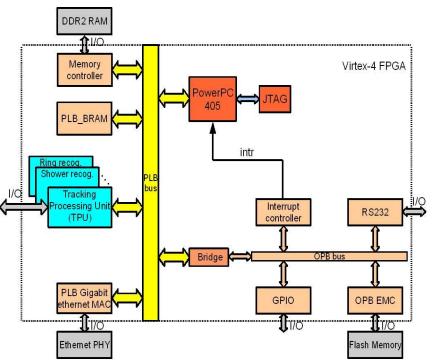

### **FPGA Node Development**

- Old bus-based architecture (PLB & OPB)

- CPU & Fast peripherals on PLB

- Slow peripherals on OPB

- Tracking Processing Unit (TPU) on PLB as a fast device

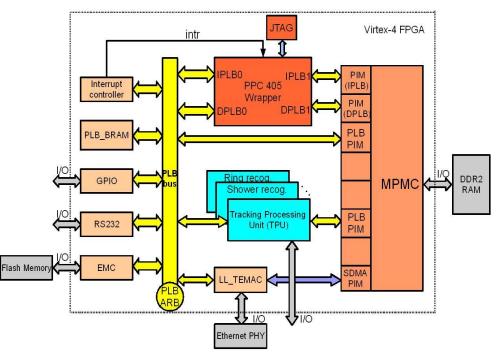

- New LocalLink-based architecture

- Multi-Port Memory Controller (8 ports)

- Direct access to the memory from the device

- TPU interfaced to MPMC directly

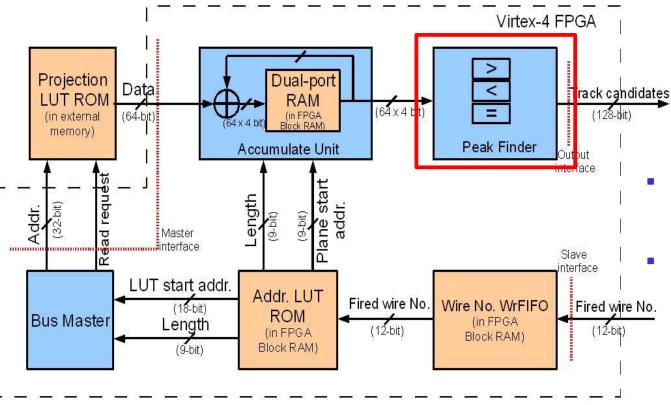

- Tracking Processing Unit (TPU) for track reconstruction computation

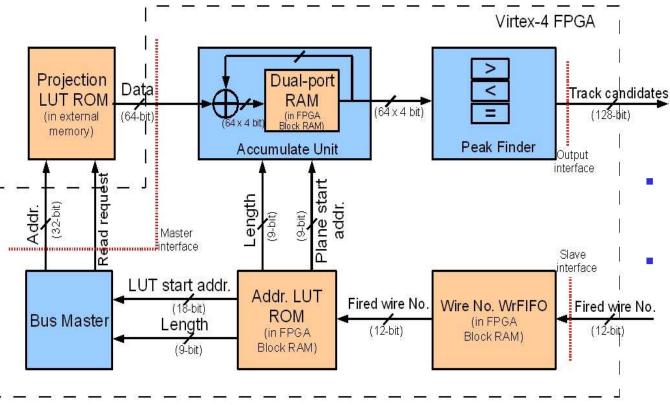

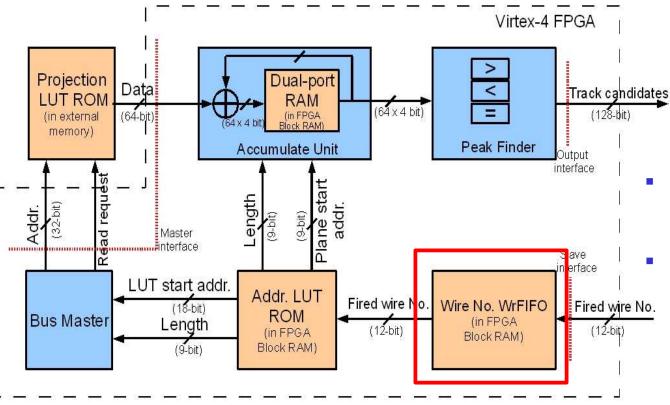

- Sub-modules:

- Wire No. Write FIFO

- Proj. LUT & Addr. LUT

- Bus master

- Accumulate unit

- Peak finder

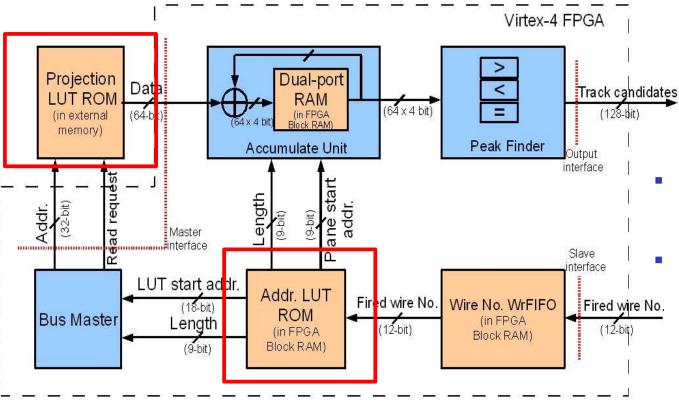

- Tracking Processing Unit (TPU) for track reconstruction computation

- Sub-modules:

- Wire No. Write FIFO

- Proj. LUT & Addr. LUT

- Bus master

- Accumulate unit

- Peak finder

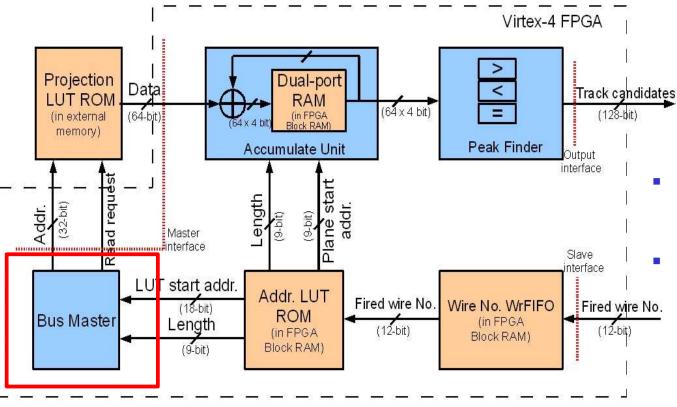

- Tracking Processing Unit (TPU) for track reconstruction computation

- Sub-modules:

- Wire No. Write FIFO

- Proj. LUT & Addr. LUT

- Bus master

- Accumulate unit

- Peak finder

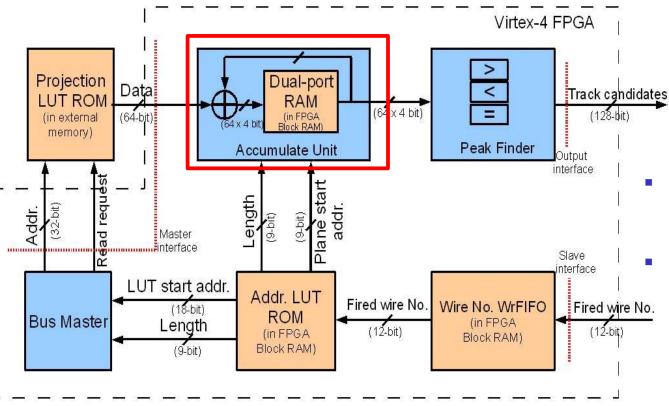

- Tracking Processing Unit (TPU) for track reconstruction computation

- Sub-modules:

- Wire No. Write FIFO

- Proj. LUT & Addr. LUT

- Bus master

- Accumulate unit

- Peak finder

- Tracking Processing Unit (TPU) for track reconstruction computation

- Sub-modules:

- Wire No. Write FIFO

- Proj. LUT & Addr. LUT

- Bus master

- Accumulate unit

- Peak finder

- Tracking Processing Unit (TPU) for track reconstruction computation

- Sub-modules:

- Wire No. Write FIFO

- Proj. LUT & Addr. LUT

- Bus master

- Accumulate unit

- Peak finder

### **Implementation Results**

| Resources            | TPU                             | compute node<br>platform     | PLB-IPIF                       | system with<br>TPU (sum)         |

|----------------------|---------------------------------|------------------------------|--------------------------------|----------------------------------|

| 4-input<br>LUTs      | 5175 out<br>of 50560<br>(10.2%) | 8531 out of<br>50560 (16.9%) | 2900 out<br>of 50560<br>(5.7%) | 16606 out<br>of 50560<br>(32.8%) |

| Slice Flip-<br>Flops | 1715 out<br>of 50560<br>(3.4%)  | 5724 out of<br>50560 (11.3%) | 1640 out<br>of 50560<br>(3.2%) | 9079 out<br>of 50560<br>(18.0%)  |

| Block<br>RAMs        | 41 out of 232 (17.7%)           | 18 out of 232<br>(7.8%)      | 0                              | 59 out of 232<br>(25.4%)         |

| DSP<br>Slices        | 0                               | 8 out of 128<br>(6.3%)       | 0                              | 8 out of 128<br>(6.3%)           |

#### Table 1. Resource consumption

- Resource utilization of Virtex-4 FX60 FPGA -- acceptable!

- Timing limitation: 125 MHz without much optimization effort

- Clock frequency fixed at 100 MHz, to match the PLB speed

### **Performance Evaluation**

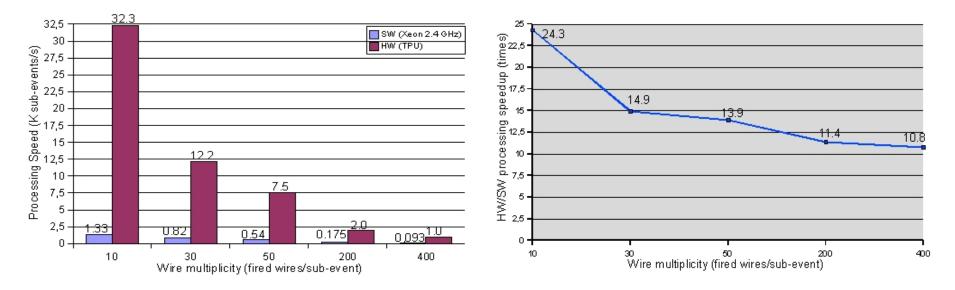

- MPMC-based structure used for measurements

- A C program running on the Xeon 2.4 GHz computer as the software reference

- Different measurement points on different wire multiplicities (10, 30, 50, 200, 400 fired wires out of 2110)

- Speedup of 10.8-24.3 times per module have been seen compared to the software solution.

### **Conclusion and Future Work**

- Basic principle of the inner track reconstruction for particle physics experiments was implemented on Xilinx FPGA.

- Integrated in the system design, the TPU module works to find out track candidates.

- Resource utilization is acceptable. The speedup of 10.8-24.3 times per module has been seen, compared to the software solution.

- Incorporate multiple modules in the system and make them work in parallel for high performance.

- Outer tracking implementation.

# Thanks for your attention!