|

A configurable on-chip network platform is developed with VHDL during his PhD work. The platform exploits the

adaptive router described in Chapter 4 of the thesis

(

download here) where the router is configurable to use different routing protocols presented in Chapter 3 of

the book. It employs the network interface described in Chapter 5 to connect AXI-based processors to the network.

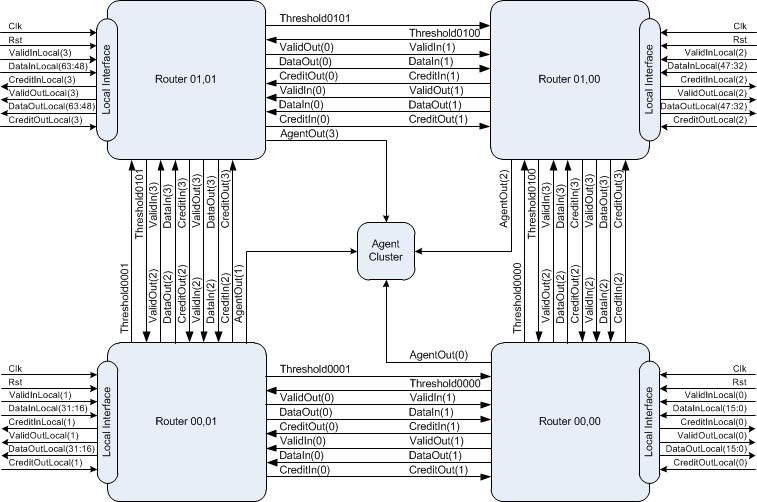

Here, a lightweight prototype of the platform is presented. As illustrated in Fig. A-1, the prototype is composed of

four routers each of which contains an AXI-based network interface. The agent cluster adjusts the frequency and voltage

based on the congestion value.

Fig. A-1. The test chip architecture.

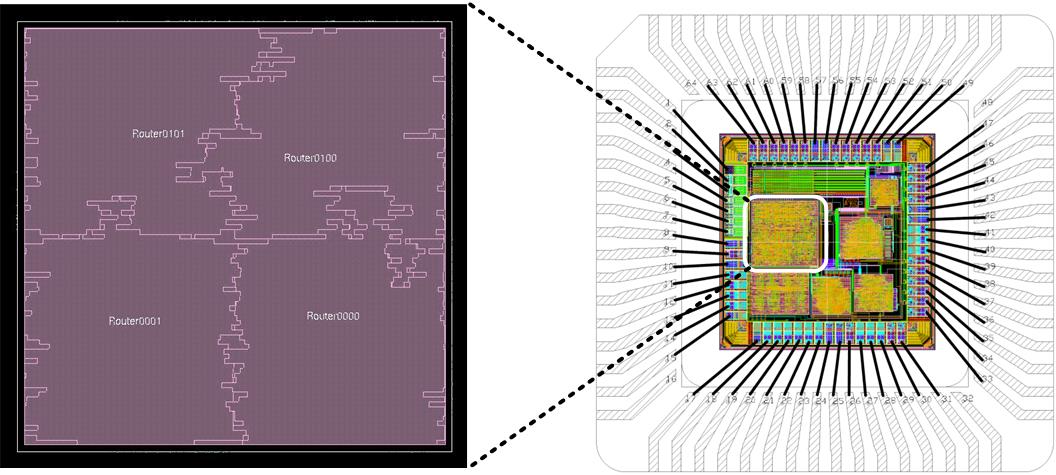

The VHDL implementation of the platform is simulated using the ModelSim simulator from Mentor graphic and synthesized

by Synopsys Design Compiler. Different tools from Synopsys (for frontend) and Cadence (for backend), e.g. Synopsys Design

Compiler, Synopsys PrimePower, Cadence Encounter, and Cadence Virtuoso, are used for hardware analysis and layout. A test

chip from the lightweight platform (Fig. A-1) was fabricated using the ST 65nm CMOS technology with Low Power Low Voltage

Standard Cell Library at 1 V supply voltage. The hardware layout of the platform is shown in Fig. A-2. The 0.07mm2 design

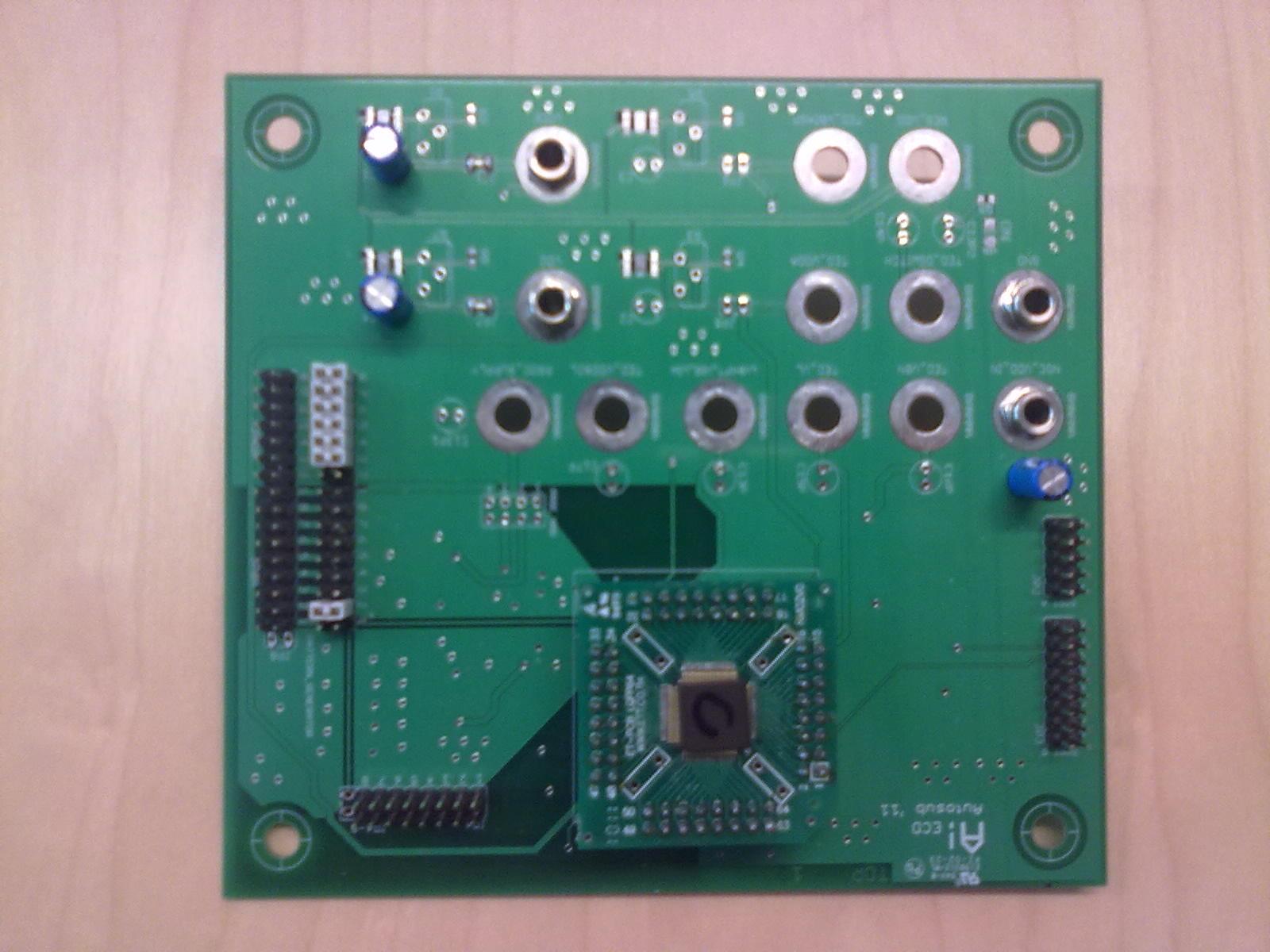

contains 5520 cells along with 146 IOs with chip maximum operating frequency of 2 GHz. Finally, Fig. A-3 depicts the

targeted prototype board. The platform is supposed to connect four AXI-based processors while voltage and frequency are

adapted based on the agent decision integrated in the network.

Fig. A-2. The test chip layout.

Fig. A-3. The prototype board.

Board manuals can be downloaded from

here.

Chip manual can be downloaded from

here.

|