Studies of classical HPC problems on fine-grained and massively parallel computing environment based on reconfigurable hardware.

Evaluation of an FPGA-based supercomputing platform

## LAURENZ CHRISTIAN BURI

Master of Science Thesis Stockholm, Sweden 2006

ICT/LECS-2006-88

Studies of classical HPC problems on fine-grained and massively parallel computing environment based on reconfigurable hardware.

Evaluation of an FPGA-based supercomputing platform

### LAURENZ CHRISTIAN BURI

Supervisor Olle Raab Mitrionics AB, Lund, Sweden

Examiner Vladimir Vlassov Department of Microelectronics and Information Technology IMIT KTH, Stockholm, Sweden

Master of Science Thesis Stockholm, Sweden 2006

ICT/LECS-2006-88

#### Abstract

Today, High Performance Computing (HPC) problems occur in various lines of business. Whilst conventional von Neumann processors are slowly approaching the maximum of feasible CPU frequency, become FPGA's an interesting alternative as they get large enough to be able to implement critical algorithms efficiently.

This thesis consists of an evaluation of the capabilities of the FPGA based supercomputing platform Mitrion regarding mathematical functions, ranging from linear algebra to trigonometry. The evaluation illuminates the achievable speed-up as well as the programmability of the reconfigurable processor and compares these aspects with ANSI-C solutions destined for an ordinary x86 AMD 64 processor.

For a short summary of the overall results please refer directly to chapter 10.

Keywords : Mitrion, HPC, FPGA

#### Acknowledgements

The realization of this Master thesis at Mitrionics was both fun and a highly valuable knowledge enrichment. It was very interesting to work with their intelligent product, which adds cutting edge technology to the supercomputing world.

I would like to thank everybody at Mitrionics, especially my supervisor Olle Raab, for having supported me in realizing this diploma work. I would also like to thank my examiner, Vlad Vlassov, for help with the report and administration. Last but not least I thank my opponent, Piotr Kundu, for useful inputs, which helped me to improve the quality of this report.

# Contents

| Li       | st of             | Figures                                                                          | 1             |

|----------|-------------------|----------------------------------------------------------------------------------|---------------|

| 1        | Intr              | roduction                                                                        | 3             |

|          | 1.1               | Preamble                                                                         | 3             |

|          | 1.2               | Project specification                                                            | 3             |

|          | 1.3               | Mitrionics                                                                       | 4             |

|          | 1.4               | Assumed prior knowledge                                                          | 4             |

|          | 1.5               | Reading directions                                                               | 4             |

|          | 1.6               | Related work                                                                     | 4             |

|          | 1.7               | High Performance Computing                                                       | 5             |

|          | 1.8               | The von Neumann machine                                                          | 5             |

|          | 1.9               | Limitations of the von Neumann model                                             | 5             |

|          | 1.10              | Benchmarking                                                                     | 6             |

| 0        | <b>D</b>          | · · · · · · · · · · · · · · · · · · ·                                            | 7             |

| <b>2</b> | <b>Das</b><br>2.1 | ic terms and concepts of parallel computing<br>Motivation for parallel computing | 7             |

|          | $\frac{2.1}{2.2}$ | Complexity notations                                                             | $\frac{1}{7}$ |

|          | $\frac{2.2}{2.3}$ | Data dependency                                                                  | 7             |

|          | 2.5               | 2.3.1       Critical path                                                        | 8             |

|          | 2.4               |                                                                                  | 8             |

|          | 2.4               | Speedup                                                                          | 8<br>9        |

|          | 2.5               |                                                                                  | 9<br>9        |

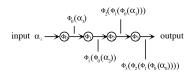

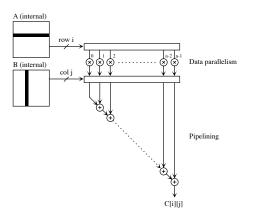

|          | 2.0               | Achieving parallelism         2.5.1       Pipelining                             | 9             |

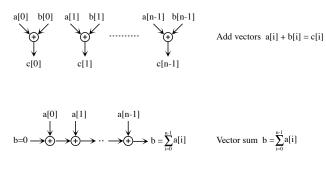

|          |                   | 2.5.1Pipelining2.5.2Data-parallelism                                             | 9<br>10       |

|          | 2.6               | 1                                                                                | $10 \\ 10$    |

|          | 2.0               | Granularity                                                                      | 10            |

| 3        | Mit               | rion - The virtual processor                                                     | <b>13</b>     |

|          | 3.1               | The Mitrion processor                                                            | 13            |

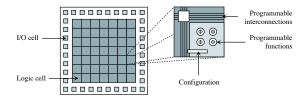

|          | 3.2               | Reconfigurable hardware                                                          | 13            |

|          |                   | 3.2.1 FPGA                                                                       | 14            |

|          |                   | Vendors                                                                          | 14            |

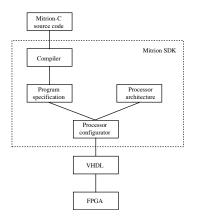

|          | 3.3               | The Mitrion SDK                                                                  | 14            |

|          |                   | 3.3.1 Development process                                                        | 14            |

|          |                   | 3.3.2 Target platforms                                                           | 15            |

|          | 3.4               | The programming language Mitrion-C                                               | 16            |

|          |                   | 3.4.1 Types and Assignments                                                      | 16            |

|          |                   | Scalar types                                                                     | 16            |

|          |                   | Assignment                                                                       | 16            |

|   |              | Collection Types $\ldots$                      | 17              |

|---|--------------|------------------------------------------------|-----------------|

|   |              | 3.4.2 Dependency and functional aspect         | 17              |

|   |              | 3.4.3 Loops                                    | 17              |

|   |              | Foreach loop                                   | 17              |

|   |              | For loop                                       | 17              |

|   |              | While loop                                     | 17              |

|   |              | 3.4.4 Example: Fibonacci sequence              | 17              |

|   |              | 3.4.5 Memory management                        | 18              |

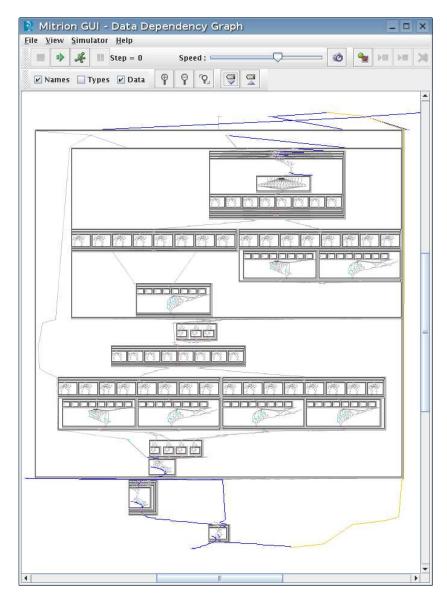

|   | 3.5          | Graphical debugger                             | 18              |

|   | 0.0          | arapinoar accu6801                             | 10              |

| 4 | Ma           | trix multiplication                            | 19              |

|   | 4.1          | Matrix multiplication                          | 19              |

|   |              | 4.1.1 Complexity                               | 19              |

|   | 4.2          | Implementation in Mitrion-C                    | 20              |

|   |              | 4.2.1 Small square matrices                    | 20              |

|   |              | 4.2.2 High dimensioned square matrices         | 21              |

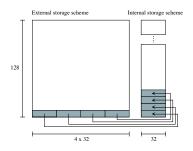

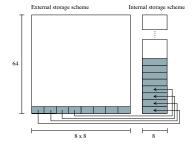

|   |              | 4.2.3 Matrix preloading                        | $\frac{21}{22}$ |

|   |              | 4.2.4 Exploit the FPGA to full capacity        | $\frac{22}{22}$ |

|   | 4.3          | Performance                                    | $\frac{22}{22}$ |

|   | 4.4          |                                                | 22              |

|   | 4.4          | Summary                                        | 20              |

| 5 | Gai          | ussian elimination                             | 25              |

| Ŭ | 5.1          | Introduction to Gaussian elimination           | 25              |

|   | 5.2          | Basic algorithm                                | $\frac{20}{25}$ |

|   | 0.2          | 5.2.1 Partial pivoting                         | 25              |

|   |              | 5.2.2 Complexity                               | 26<br>26        |

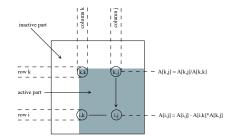

|   | 5.3          | Parallelization                                | 20<br>26        |

|   | 5.3<br>5.4   | Implementation on the Mitrion platform         | 20<br>27        |

|   | $5.4 \\ 5.5$ | Alternative solutions                          | $\frac{27}{27}$ |

|   | 0.0          | 5.5.1 LU factorization                         | $\frac{21}{27}$ |

|   |              |                                                | 21              |

|   | E C          |                                                |                 |

|   | 5.6          | Result                                         | 28              |

| 6 | Iac          | obi's linear equation solver                   | 29              |

| U | 6.1          | Motivation for Jacobi's linear equation solver | 29              |

|   | 6.2          | Overview of the Jacobi method                  | 29<br>29        |

|   | 0.2          |                                                | 29<br>30        |

|   |              | 6.2.1 Convergence criteria                     |                 |

|   | <i>c</i>     | 6.2.2 Complexity                               | 30              |

|   | 6.3          | Implementation design                          | 30              |

|   | 6.4          | Jacobi iterations on a single processor        | 31              |

|   | 6.5          | Performance                                    | 32              |

|   | 6.6          | Related projects                               | 32              |

|   | 6.7          | Conclusion                                     | 33              |

|   | 6.8          | Summary                                        | 33              |

| _ | р.           |                                                | <b></b>         |

| 7 |              | 0 1                                            | 35              |

|   | 7.1          |                                                | 35              |

|   | 7.2          | The Haar wavelet transformation                | 36              |

|   | 7.3          | Thresholding and lossy transformation          | 37              |

|   | 7.4          | Implementation design                          | 37              |

| 1.1.1       Integrit of the state of the st                                                                                                                                    | 7.4.2       Data flow       38         7.5       Resource usage       39         7.6       Performance       39         7.7       Summary       39         8       CORDIC       41         8.1       Overview of CORDIC       41         8.2       Sine and cosine calculation       41         8.2.1       Precision of CORDIC       43         8.3.1       Implementation design       43         8.3.2       Pipelining versus data-parallelism       43         8.3.3       Unsolved problems       45         8.4       Performance       45         8.5       Summary       45         9       Discussion       47         9.1       FPGA based platforms       47         9.2       Hardware design process       47         9.3       Controlling resource usage       48         9.4       Dynamic of Mitrion-C       49         9.5       Memory management       48         9.6       Appropriate algorithms for Mitrion-C       49         9.7       Dynamic of Mitrion-C       53         10       Conclusions       51         11       Future work       <                                                          |              |       | 7.4.1 Integer to integer transformation | 37 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------|-----------------------------------------|----|

| 7.5       Resource usage       39         7.6       Performance       39         7.7       Summary       39         8       CORDIC       41         8.1       Overview of CORDIC       41         8.2       Sine and cosine calculation       43         8.3       Implementation design       43         8.3.1       Parallelism       43         8.3.2       Pipelining versus data-parallelism       43         8.3.3       Unsolved problems       45         8.4       Performance       45         8.5       Summary       45         9       Discussion       47         9.1       FPGA based platforms       47         9.2       Hardware design process       47         9.3       Controlling resource usage       48         9.4       Dynamic of Mitrion-C       48         9.5       Memory management       48         9.6       Appropriate algorithms for Mitrion-C       49         9.8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7.5       Resource usage       39         7.6       Performance       39         7.7       Summary       39         8       CORDIC       41         8.1       Overview of CORDIC       41         8.2       Sine and cosine calculation       41         8.2       Sine and cosine calculation       41         8.2.1       Precision of CORDIC       43         8.3       Implementation design       43         8.3.1       Parallelism       43         8.3.2       Pipelining versus data-parallelism       43         8.3.3       Unsolved problems       45         8.4       Performance       45         8.5       Summary       45         9       Discussion       47         9.1       FPGA based platforms       47         9.2       Hardware design process       47         9.3       Controlling resource usage       48         9.4       Dynamic of Mitrion-C       48         9.5       Memory management       48         9.6       Appropriate algorithms for Mitrion-C       49         9.8       Portability       50         9.9       Performance res                                                     |              |       |                                         |    |

| 7.6       Performance       39         7.7       Summary       39         8       CORDIC       41         8.1       Overview of CORDIC       41         8.2       Sine and cosine calculation       41         8.2       Sine and cosine calculation       41         8.2       Sine and cosine calculation       41         8.3       Implementation design       43         8.3.1       Parallelism       43         8.3.2       Pipelining versus data-parallelism       43         8.3.3       Unsolved problems       45         8.4       Performance       45         8.5       Summary       45         9       Discussion       47         9.1       FPGA based platforms       47         9.2       Hardware design process       47         9.3       Controlling resource usage       48         9.4       Dynamic of Mitrion-C       48         9.5       Memory management       48         9.6       Appropriate algorithms for Mitrion-C       49         9.7       Dynamic bit-width       49         9.8       Portability       50         9.9       Perfor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7.6       Performance       39         7.7       Summary       39         8       CORDIC       41         8.1       Overview of CORDIC       41         8.2       Sine and cosine calculation       41         8.2       Sine and cosine calculation       41         8.2       Sine and cosine calculation       41         8.3       Implementation design       43         8.3.1       Parallelism       43         8.3.2       Pipelining versus data-parallelism       43         8.3.3       Unsolved problems       45         8.4       Performance       45         8.5       Summary       45         9       Discussion       47         9.1       FPGA based platforms       47         9.2       Hardware design process       47         9.3       Controlling resource usage       48         9.4       Dynamic of Mitrion-C       48         9.5       Memory management       48         9.6       Appropriate algorithms for Mitrion-C       49         9.7       Dynamic bit-width       50         9.8       Portability       50         9.9       Perfor                                                     |              | 7.5   |                                         |    |

| 7.7       Summary       39         8       CORDIC       41         8.1       Overview of CORDIC       41         8.2       Sine and cosine calculation       41         8.2.1       Precision of CORDIC       43         8.3       Implementation design       43         8.3.1       Parallelism       43         8.3.2       Pipelining versus data-parallelism       43         8.3.3       Unsolved problems       45         8.5       Summary       45         9       Discussion       47         9.1       FPGA based platforms       47         9.2       Hardware design process       47         9.3       Controlling resource usage       48         9.4       Dynamic of Mitrion-C       48         9.5       Memory management       48         9.6       Appropriate algorithms for Mitrion-C       49         9.8       Portability       50         9.9       Performance results resumed       50         9.9       Performance results resumed       50         10       Conclusions       51         11       Future work       53         11.1       Dyn                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7.7       Summary       39         8       CORDIC       41         8.1       Overview of CORDIC       41         8.2       Sine and cosine calculation       41         8.2       Sine and cosine calculation       41         8.2       Sine and cosine calculation       43         8.3.1       Precision of CORDIC       43         8.3.1       Parallelism       43         8.3.1       Parallelism       43         8.3.2       Pipelining versus data-parallelism       43         8.3.3       Unsolved problems       45         8.4       Performance       45         8.5       Summary       45         9       Discussion       47         9.1       FPGA based platforms       47         9.2       Hardware design process       47         9.3       Controlling resource usage       48         9.4       Dynamic of Mitrion-C       49         9.5       Memory management       48         9.6       Appropriate algorithms for Mitrion-C       49         9.7       Dynamic bit-width       49         9.8       Portability       50         9.9       Perf                                                     |              |       | 0                                       |    |

| 8.1       Overview of CORDIC       41         8.2       Sine and cosine calculation       41         8.2.1       Precision of CORDIC       43         8.3       Implementation design       43         8.3.1       Parallelism       43         8.3.2       Pipelining versus data-parallelism       43         8.3.3       Unsolved problems       45         8.4       Performance       45         8.5       Summary       45         9       Discussion       47         9.1       FPGA based platforms       47         9.2       Hardware design process       47         9.3       Controlling resource usage       48         9.4       Dynamic of Mitrion-C       48         9.5       Memory management       48         9.6       Appropriate algorithms for Mitrion-C       49         9.7       Dynamic bit-width       49         9.8       Portability       50         9.9       Performance results resumed       50         10       Conclusions       51         11       Future work       53         11.3       Memory simulation       54         11.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 8.1       Overview of CORDIC       41         8.2       Sine and cosine calculation       41         8.2.1       Precision of CORDIC       43         8.3       Implementation design       43         8.3.1       Parallelism       43         8.3.2       Pipelining versus data-parallelism       43         8.3.3       Unsolved problems       45         8.4       Performance       45         8.5       Summary       45         9       Discussion       47         9.1       FPGA based platforms       47         9.2       Hardware design process       47         9.3       Controlling resource usage       48         9.4       Dynamic of Mitrion-C       48         9.5       Memory management       48         9.6       Appropriate algorithms for Mitrion-C       49         9.7       Dynamic bit-width       50         9.8       Portability       50         9.9       Performance results resumed       50         10       Conclusions       51         11       Future work       53         11.1       Dynamic of Mitrion-C       53         11.2                                                    |              |       |                                         |    |

| 8.1       Overview of CORDIC       41         8.2       Sine and cosine calculation       41         8.2.1       Precision of CORDIC       43         8.3       Implementation design       43         8.3.1       Parallelism       43         8.3.2       Pipelining versus data-parallelism       43         8.3.3       Unsolved problems       45         8.4       Performance       45         8.5       Summary       45         9       Discussion       47         9.1       FPGA based platforms       47         9.2       Hardware design process       47         9.3       Controlling resource usage       48         9.4       Dynamic of Mitrion-C       48         9.5       Memory management       48         9.6       Appropriate algorithms for Mitrion-C       49         9.7       Dynamic bit-width       49         9.8       Portability       50         9.9       Performance results resumed       50         10       Conclusions       51         11       Future work       53         11.3       Memory simulation       54         11.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 8.1       Overview of CORDIC       41         8.2       Sine and cosine calculation       41         8.2.1       Precision of CORDIC       43         8.3       Implementation design       43         8.3.1       Parallelism       43         8.3.2       Pipelining versus data-parallelism       43         8.3.3       Unsolved problems       45         8.4       Performance       45         8.5       Summary       45         9       Discussion       47         9.1       FPGA based platforms       47         9.2       Hardware design process       47         9.3       Controlling resource usage       48         9.4       Dynamic of Mitrion-C       48         9.5       Memory management       48         9.6       Appropriate algorithms for Mitrion-C       49         9.7       Dynamic bit-width       50         9.8       Portability       50         9.9       Performance results resumed       50         10       Conclusions       51         11       Future work       53         11.1       Dynamic of Mitrion-C       53         11.2                                                    | 0            | GOI   |                                         |    |

| 8.2       Sine and cosine calculation       41         8.2.1       Precision of CORDIC       43         8.3       Implementation design       43         8.3.1       Parallelism       43         8.3.2       Pipelining versus data-parallelism       43         8.3.3       Unsolved problems       45         8.4       Performance       45         8.5       Summary       45         9       Discussion       47         9.1       FPGA based platforms       47         9.2       Hardware design process       47         9.3       Controlling resource usage       48         9.4       Dynamic of Mitrion-C       48         9.5       Memory management       48         9.6       Appropriate algorithms for Mitrion-C       49         9.7       Dynamic bit-width       49         9.8       Portability       50         9.9       Performance results resumed       50         10       Conclusions       51         11       Future work       53         11.1       Dynamic of Mitrion-C       53         11.2       JPEG 2000       53         11.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 8.2       Sine and cosine calculation       41         8.2.1       Precision of CORDIC       43         8.3       Implementation design       43         8.3.1       Parallelism       43         8.3.2       Pipelining versus data-parallelism       43         8.3.3       Unsolved problems       43         8.3.4       Performance       45         8.5       Summary       45         9       Discussion       47         9.1       FPGA based platforms       47         9.2       Hardware design process       47         9.3       Controlling resource usage       48         9.4       Dynamic of Mitrion-C       48         9.5       Memory management       49         9.6       Appropriate algorithms for Mitrion-C       49         9.7       Dynamic bit-width       49         9.8       Portability       50         9.9       Performance results resumed       50         10       Conclusions       51         11       Future work       53         11.1       Dynamic of Mitrion-C       53         11.2       JPEG 2000       53         11.3 <t< th=""><th>8</th><th></th><th></th><th></th></t<>     | 8            |       |                                         |    |

| 8.2.1       Precision of CORDIC       43         8.3       Implementation design       43         8.3.1       Parallelism       43         8.3.2       Pipelining versus data-parallelism       43         8.3.3       Unsolved problems       45         8.4       Performance       45         8.5       Summary       45         9       Discussion       47         9.1       FPGA based platforms       47         9.2       Hardware design process       47         9.3       Controlling resource usage       48         9.4       Dynamic of Mitrion-C       48         9.5       Memory management       48         9.6       Appropriate algorithms for Mitrion-C       49         9.7       Dynamic bit-width       49         9.8       Portability       50         9.9       Performance results resumed       50         10       Conclusions       51         11       Future work       53         11.1       Dynamic of Mitrion-C       53         11.2       JPEG 2000       53         11.3       Memory simulation       54         11.4       Memory to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 8.2.1       Precision of CORDIC       43         8.3       Implementation design       43         8.3.1       Parallelism       43         8.3.2       Pipelining versus data-parallelism       43         8.3.3       Unsolved problems       45         8.4       Performance       45         8.5       Summary       45         9       Discussion       47         9.1       FPGA based platforms       47         9.2       Hardware design process       47         9.3       Controlling resource usage       48         9.4       Dynamic of Mitrion-C       48         9.5       Memory management       48         9.6       Appropriate algorithms for Mitrion-C       49         9.7       Dynamic bit-width       49         9.8       Portability       50         9.9       Performance results resumed       50         10       Conclusions       51         11       Future work       53         11.1       Dynamic of Mitrion-C       53         11.2       JPEG 2000       53         11.3       Memory simulation       54         11.6       Compariso                                                     |              | -     |                                         |    |

| 8.3       Implementation design       43         8.3.1       Parallelism       43         8.3.2       Pipelining versus data-parallelism       43         8.3.3       Unsolved problems       45         8.4       Performance       45         8.5       Summary       45         9       Discussion       47         9.1       FPGA based platforms       47         9.2       Hardware design process       47         9.3       Controlling resource usage       48         9.4       Dynamic of Mitrion-C       48         9.5       Memory management       49         9.6       Appropriate algorithms for Mitrion-C       49         9.7       Dynamic bit-width       49         9.8       Portability       50         9.9       Performance results resumed       50         10       Conclusions       51         11       Future work       53         11.1       Dynamic of Mitrion-C       53         11.2       JPEG 2000       53         11.3       Memory simulation       54         11.4       Memory token handling       54         11.6       Comparis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 8.3       Implementation design       43         8.3.1       Parallelism       43         8.3.2       Pipelining versus data-parallelism       43         8.3.3       Unsolved problems       45         8.4       Performance       45         8.5       Summary       45         9       Discussion       47         9.1       FPGA based platforms       47         9.2       Hardware design process       47         9.3       Controlling resource usage       48         9.4       Dynamic of Mitrion-C       48         9.5       Memory management       48         9.6       Appropriate algorithms for Mitrion-C       48         9.6       Appropriate algorithms for Mitrion-C       49         9.7       Dynamic bit-width       49         9.8       Portability       50         9.9       Performance results resumed       50         10       Conclusions       51         11       Future work       53         11.1       Dynamic of Mitrion-C       53         11.2       JPEG 2000       53         11.3       Memory simulation       54         11.6                                                      |              | 0.2   |                                         |    |

| 8.3.1       Parallelism       43         8.3.2       Pipelining versus data-parallelism       43         8.3.3       Unsolved problems       45         8.4       Performance       45         8.5       Summary       45         9       Discussion       47         9.1       FPGA based platforms       47         9.2       Hardware design process       47         9.3       Controlling resource usage       48         9.4       Dynamic of Mitrion-C       48         9.5       Memory management       48         9.6       Appropriate algorithms for Mitrion-C       49         9.7       Dynamic bit-width       49         9.8       Portability       50         9.9       Performance results resumed       50         9.9       Performance results resumed       50         10       Conclusions       51         11.1       Dynamic of Mitrion-C       53         11.2       JPEG 2000       53         11.3       Memory simulation       54         11.4       Memory token handling       54         11.5       Resource usage optimization       54         11.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 8.3.1       Parallelism       43         8.3.2       Pipelining versus data-parallelism       43         8.3.3       Unsolved problems       45         8.4       Performance       45         8.5       Summary       45         9       Discussion       47         9.1       FPGA based platforms       47         9.2       Hardware design process       47         9.3       Controlling resource usage       48         9.4       Dynamic of Mitrion-C       48         9.5       Memory management       48         9.6       Appropriate algorithms for Mitrion-C       49         9.7       Dynamic bit-width       49         9.8       Portability       50         9.9       Performance results resumed       50         10       Conclusions       51         11       Future work       53         11.1       Dynamic of Mitrion-C       53         11.2       JPEG 2000       53         11.3       Memory simulation       54         11.4       Memory token handling       54         11.5       Resource usage optimization       54         11.6       C                                                     |              | 83    |                                         |    |

| 8.3.2       Pipelining versus data-parallelism       43         8.3.3       Unsolved problems       45         8.4       Performance       45         8.5       Summary       45         9       Discussion       47         9.1       FPGA based platforms       47         9.2       Hardware design process       47         9.3       Controlling resource usage       48         9.4       Dynamic of Mitrion-C       48         9.5       Memory management       48         9.6       Appropriate algorithms for Mitrion-C       49         9.7       Dynamic bit-width       49         9.8       Portability       50         9.9       Performance results resumed       50         9.9       Performance results resumed       50         10       Conclusions       51         11       Future work       53         11.1       Dynamic of Mitrion-C       53         11.2       JPEG 2000       53         11.3       Memory simulation       54         11.4       Memory token handling       54         11.5       Resource usage optimization       54         11.6 <th>8.3.2       Pipelining versus data-parallelism       43         8.3.3       Unsolved problems       45         8.4       Performance       45         8.5       Summary       45         9       Discussion       47         9.1       FPGA based platforms       47         9.2       Hardware design process       47         9.3       Controlling resource usage       48         9.4       Dynamic of Mitrion-C       48         9.5       Memory management       48         9.6       Appropriate algorithms for Mitrion-C       49         9.7       Dynamic bit-width       49         9.8       Portability       50         9.9       Performance results resumed       50         9.9       Performance results resumed       50         10       Conclusions       51         11       Future work       53         11.1       Dynamic of Mitrion-C       53         11.2       JPEG 2000       53         11.3       Memory simulation       54         11.4       Memory token handling       54         11.5       Resource usage optimization       54         11.6<th></th><th>0.0</th><th></th><th></th></th> | 8.3.2       Pipelining versus data-parallelism       43         8.3.3       Unsolved problems       45         8.4       Performance       45         8.5       Summary       45         9       Discussion       47         9.1       FPGA based platforms       47         9.2       Hardware design process       47         9.3       Controlling resource usage       48         9.4       Dynamic of Mitrion-C       48         9.5       Memory management       48         9.6       Appropriate algorithms for Mitrion-C       49         9.7       Dynamic bit-width       49         9.8       Portability       50         9.9       Performance results resumed       50         9.9       Performance results resumed       50         10       Conclusions       51         11       Future work       53         11.1       Dynamic of Mitrion-C       53         11.2       JPEG 2000       53         11.3       Memory simulation       54         11.4       Memory token handling       54         11.5       Resource usage optimization       54         11.6 <th></th> <th>0.0</th> <th></th> <th></th>    |              | 0.0   |                                         |    |

| 8.3.3       Unsolved problems       45         8.4       Performance       45         8.5       Summary       45         9       Discussion       47         9.1       FPGA based platforms       47         9.2       Hardware design process       47         9.3       Controlling resource usage       48         9.4       Dynamic of Mitrion-C       48         9.5       Memory management       48         9.6       Appropriate algorithms for Mitrion-C       49         9.7       Dynamic bit-width       49         9.8       Portability       50         9.9       Performance results resumed       50         10       Conclusions       51         11       Future work       53         11.1       Dynamic of Mitrion-C       53         11.2       JPEG 2000       53         11.3       Memory simulation       54         11.4       Memory token handling       54         11.5       Resource usage optimization       54         11.6       Comparison with OpenMP and MPI       54         11.7       Financial aspect       54         Bibliography                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 8.3.3       Unsolved problems       45         8.4       Performance       45         8.5       Summary       45         9       Discussion       47         9.1       FPGA based platforms       47         9.2       Hardware design process       47         9.3       Controlling resource usage       48         9.4       Dynamic of Mitrion-C       48         9.5       Memory management       48         9.6       Appropriate algorithms for Mitrion-C       49         9.7       Dynamic bit-width       49         9.8       Portability       50         9.9       Performance results resumed       50         9.9       Performance results resumed       50         10       Conclusions       51         11       Future work       53         11.1       Dynamic of Mitrion-C       53         11.2       JPEG 2000       53         11.3       Memory simulation       54         11.4       Memory token handling       54         11.5       Resource usage optimization       54         11.6       Comparison with OpenMP and MPI       54         11.7                                                    |              |       |                                         |    |

| 8.4       Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 8.4       Performance       45         8.5       Summary       45         9       Discussion       47         9.1       FPGA based platforms       47         9.2       Hardware design process       47         9.3       Controlling resource usage       48         9.4       Dynamic of Mitrion-C       48         9.5       Memory management       48         9.6       Appropriate algorithms for Mitrion-C       49         9.7       Dynamic bit-width       49         9.8       Portability       50         9.9       Performance results resumed       50         9.9       Performance results resumed       50         10       Conclusions       51         11       Future work       53         11.1       Dynamic of Mitrion-C       53         11.2       JPEG 2000       53         11.3       Memory simulation       54         11.4       Memory token handling       54         11.5       Resource usage optimization       54         11.6       Comparison with OpenMP and MPI       54         11.7       Financial aspect       54         Bibliography </th <th></th> <th></th> <th></th> <th></th> |              |       |                                         |    |

| 8.5       Summary       45         9       Discussion       47         9.1       FPGA based platforms       47         9.2       Hardware design process       47         9.3       Controlling resource usage       48         9.4       Dynamic of Mitrion-C       48         9.5       Memory management       48         9.6       Appropriate algorithms for Mitrion-C       49         9.7       Dynamic bit-width       49         9.8       Portability       50         9.9       Performance results resumed       50         9.9       Performance results resumed       50         10       Conclusions       51         11       Future work       53         11.1       Dynamic of Mitrion-C       53         11.2       JPEG 2000       53         11.3       Memory simulation       54         11.4       Memory token handling       54         11.5       Resource usage optimization       54         11.6       Comparison with OpenMP and MPI       54         11.7       Financial aspect       54         Bibliography       55         Index       57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 8.5       Summary       45         9       Discussion       47         9.1       FPGA based platforms       47         9.2       Hardware design process       47         9.3       Controlling resource usage       48         9.4       Dynamic of Mitrion-C       48         9.5       Memory management       48         9.6       Appropriate algorithms for Mitrion-C       49         9.7       Dynamic bit-width       49         9.8       Portability       50         9.9       Performance results resumed       50         9.9       Performance results resumed       50         10       Conclusions       51         11       Future work       53         11.1       Dynamic of Mitrion-C       53         11.2       JPEG 2000       53         11.3       Memory token handling       54         11.5       Resource usage optimization       54         11.5       Resource usage optimization       54         11.6       Comparison with OpenMP and MPI       54         11.7       Financial aspect       54         Bibliography       55         Index       5                                            |              | Q /   |                                         |    |

| 9 Discussion       47         9.1 FPGA based platforms       47         9.2 Hardware design process       47         9.3 Controlling resource usage       48         9.4 Dynamic of Mitrion-C       48         9.5 Memory management       48         9.6 Appropriate algorithms for Mitrion-C       49         9.7 Dynamic bit-width       49         9.8 Portability       50         9.9 Performance results resumed       50         10 Conclusions       51         11 Future work       53         11.1 Dynamic of Mitrion-C       53         11.2 JPEG 2000       53         11.3 Memory simulation       54         11.4 Memory token handling       54         11.5 Resource usage optimization       54         11.6 Comparison with OpenMP and MPI       54         11.7 Financial aspect       54         Bibliography       55         Index       57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 9 Discussion       47         9.1 FPGA based platforms       47         9.2 Hardware design process       47         9.3 Controlling resource usage       48         9.4 Dynamic of Mitrion-C       48         9.5 Memory management       48         9.6 Appropriate algorithms for Mitrion-C       49         9.7 Dynamic bit-width       49         9.8 Portability       50         9.9 Performance results resumed       50         9.0 Conclusions       51         11 Future work       53         11.1 Dynamic of Mitrion-C       53         11.2 JPEG 2000       53         11.3 Memory simulation       54         11.4 Memory token handling       54         11.5 Resource usage optimization       54         11.6 Comparison with OpenMP and MPI       54         11.7 Financial aspect       54         Bibliography       55         Index       57         Appendix       58                                                                                                                                                                                                                                      |              | -     |                                         |    |

| 9.1       FPGA based platforms       47         9.2       Hardware design process       47         9.3       Controlling resource usage       48         9.4       Dynamic of Mitrion-C       48         9.5       Memory management       48         9.6       Appropriate algorithms for Mitrion-C       49         9.7       Dynamic bit-width       49         9.8       Portability       50         9.9       Performance results resumed       50         10       Conclusions       51         11       Future work       53         11.1       Dynamic of Mitrion-C       53         11.2       JPEG 2000       53         11.3       Memory simulation       54         11.4       Memory token handling       54         11.5       Resource usage optimization       54         11.6       Comparison with OpenMP and MPI       54         11.7       Financial aspect       54         Bibliography       55         Index       57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 9.1       FPGA based platforms       47         9.2       Hardware design process       47         9.3       Controlling resource usage       48         9.4       Dynamic of Mitrion-C       48         9.5       Memory management       48         9.6       Appropriate algorithms for Mitrion-C       49         9.7       Dynamic bit-width       49         9.8       Portability       50         9.9       Performance results resumed       50         9.9       Performance results resumed       50         10       Conclusions       51         11       Future work       53         11.2       JPEG 2000       53         11.3       Memory simulation       54         11.4       Memory token handling       54         11.5       Resource usage optimization       54         11.6       Comparison with OpenMP and MPI       54         11.7       Financial aspect       54         Bibliography       55         Index       57         Appendix       58                                                                                                                                                   |              | 0.0   | Summary                                 | 40 |

| 9.2       Hardware design process       47         9.3       Controlling resource usage       48         9.4       Dynamic of Mitrion-C       48         9.5       Memory management       48         9.6       Appropriate algorithms for Mitrion-C       49         9.7       Dynamic bit-width       49         9.8       Portability       50         9.9       Performance results resumed       50         10       Conclusions       51         11       Future work       53         11.1       Dynamic of Mitrion-C       53         11.2       JPEG 2000       53         11.3       Memory simulation       54         11.4       Memory token handling       54         11.5       Resource usage optimization       54         11.6       Comparison with OpenMP and MPI       54         11.7       Financial aspect       54         Bibliography       55         Index       57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 9.2       Hardware design process       47         9.3       Controlling resource usage       48         9.4       Dynamic of Mitrion-C       48         9.5       Memory management       48         9.6       Appropriate algorithms for Mitrion-C       49         9.7       Dynamic bit-width       49         9.8       Portability       50         9.9       Performance results resumed       50         9.9       Performance results resumed       50         10       Conclusions       51         11       Future work       53         11.2       JPEG 2000       53         11.3       Memory simulation       54         11.4       Memory token handling       54         11.5       Resource usage optimization       54         11.6       Comparison with OpenMP and MPI       54         11.7       Financial aspect       54         Bibliography       55         Index       57         Appendix       58                                                                                                                                                                                                   | 9            | Disc  | cussion                                 | 47 |

| 9.3       Controlling resource usage       48         9.4       Dynamic of Mitrion-C       48         9.5       Memory management       48         9.6       Appropriate algorithms for Mitrion-C       49         9.7       Dynamic bit-width       49         9.8       Portability       50         9.9       Performance results resumed       50         10       Conclusions       51         11       Future work       53         11.1       Dynamic of Mitrion-C       53         11.2       JPEG 2000       53         11.3       Memory simulation       54         11.4       Memory token handling       54         11.5       Resource usage optimization       54         11.6       Comparison with OpenMP and MPI       54         11.7       Financial aspect       54         11.7       Financial aspect       54         11.6       Comparison with OpenMP and MPI       54         11.7       Financial aspect       54         11.7       Financial aspect       54         11.6       Somparison with OpenMP and MPI       54         11.7       Financial aspect       54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 9.3       Controlling resource usage       48         9.4       Dynamic of Mitrion-C       48         9.5       Memory management       48         9.6       Appropriate algorithms for Mitrion-C       49         9.7       Dynamic bit-width       49         9.8       Portability       50         9.9       Performance results resumed       50         10       Conclusions       51         11       Future work       53         11.1       Dynamic of Mitrion-C       53         11.2       JPEG 2000       53         11.3       Memory simulation       54         11.4       Memory token handling       54         11.5       Resource usage optimization       54         11.6       Comparison with OpenMP and MPI       54         11.7       Financial aspect       54         Bibliography       55         Index       57         Appendix       58                                                                                                                                                                                                                                                            |              | 9.1   | FPGA based platforms                    | 47 |

| 9.4       Dynamic of Mitrion-C       48         9.5       Memory management       48         9.6       Appropriate algorithms for Mitrion-C       49         9.7       Dynamic bit-width       49         9.8       Portability       50         9.9       Performance results resumed       50         9.9       Performance results resumed       50         10       Conclusions       51         11       Future work       53         11.2       JPEG 2000       53         11.3       Memory token handling       54         11.4       Memory token handling       54         11.5       Resource usage optimization       54         11.6       Comparison with OpenMP and MPI       54         11.7       Financial aspect       54         11.7       Financial aspect       54         11.7       Financial aspect       54         11.7       Financial aspect       55         Index       57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9.4       Dynamic of Mitrion-C       48         9.5       Memory management       48         9.6       Appropriate algorithms for Mitrion-C       49         9.7       Dynamic bit-width       49         9.8       Portability       50         9.9       Performance results resumed       50         10       Conclusions       51         11       Future work       53         11.1       Dynamic of Mitrion-C       53         11.2       JPEG 2000       53         11.3       Memory simulation       54         11.4       Memory token handling       54         11.5       Resource usage optimization       54         11.6       Comparison with OpenMP and MPI       54         11.7       Financial aspect       54         Bibliography       55         Index       57         Appendix       58                                                                                                                                                                                                                                                                                                                  |              | 9.2   | Hardware design process                 | 47 |

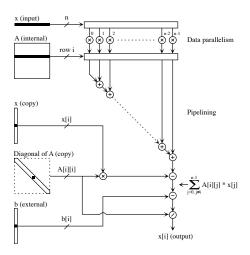

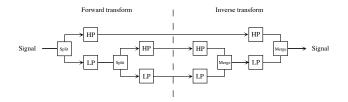

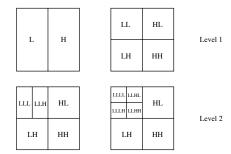

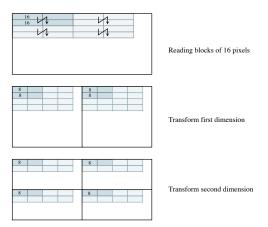

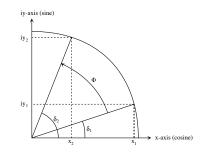

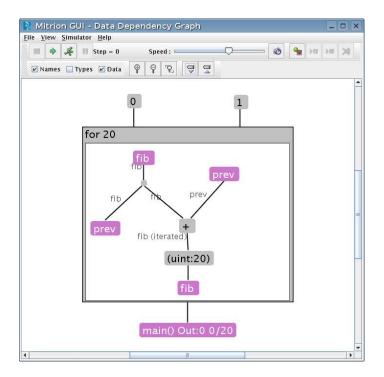

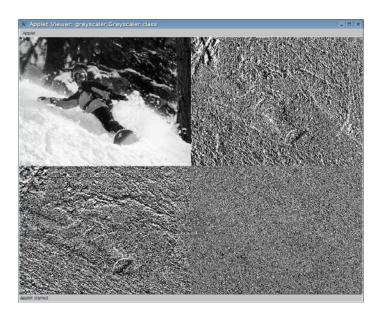

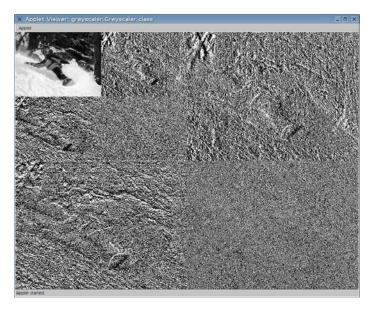

| 9.5       Memory management       48         9.6       Appropriate algorithms for Mitrion-C       49         9.7       Dynamic bit-width       49         9.8       Portability       50         9.9       Performance results resumed       50         10       Conclusions       51         11       Future work       53         11.1       Dynamic of Mitrion-C       53         11.2       JPEG 2000       53         11.3       Memory simulation       54         11.5       Resource usage optimization       54         11.6       Comparison with OpenMP and MPI       54         11.7       Financial aspect       54         11.6       Comparison with OpenMP and MPI       54         11.7       Financial aspect       54         11.6       Comparison with OpenMP and MPI       54         11.7       Financial aspect       54         11.8       State       55         Index       57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 9.5       Memory management       48         9.6       Appropriate algorithms for Mitrion-C       49         9.7       Dynamic bit-width       49         9.8       Portability       50         9.9       Performance results resumed       50         10       Conclusions       51         11       Future work       53         11.1       Dynamic of Mitrion-C       53         11.2       JPEG 2000       53         11.3       Memory simulation       54         11.4       Memory token handling       54         11.5       Resource usage optimization       54         11.6       Comparison with OpenMP and MPI       54         11.7       Financial aspect       54         Bibliography       55         Index       57         Appendix       58                                                                                                                                                                                                                                                                                                                                                                  |              | 9.3   | Controlling resource usage              | 48 |