**Christoph Wolf**

# Infrared Communication for a Wearable Computing and Communication System

**Master Thesis**

Institute for Applied Information Processing and Communications - IAIK Technical University Graz, Austria

Advisor:

Prof. Gerald Q. Maguire Jr. Computer Communication Systems Laboratory Department of Teleinformatics KTH Stockholm, Sweden

Examiner: DI Dr. Karl Christian Posch, IAIK

Graz, November 2000

© 2000 Christoph Wolf

## Abstract

Prof. Gerald Maguire, head of the Computer Communication Systems Laboratory (CCSlab) at the Department of Teleinformatics, KTH, Stockholm, Sweden and Dr. Mark. T. Smith, HP Labs, Palo Alto, California, USA have developed a slightly larger than ID-card sized wearable computer, the so-called SmartBadge. This device is designed for low power consumption and equipped with a 200 MHz RISC processor, 1 MB of FLASH and 1 MB of SRAM memory, various communication channels, audio input and output, video output, and a socket for PCMCIA cards, which allows to use for example wired or wireless network cards. In addition to this equipment, which is comparable to other PDA-like devices it also contains a variety of sensors. These sensors allow it to extend its range of possible applications by adding knowledge about the environment which can be used to provide new context- and location-aware services.

In the first chapters of this thesis I give an introduction to the hardware platform. The operation and configuration of several processor units is explained and their use is shown via a set of example routines and programs. These samples together with their explanations allows a new user to quickly write simple applications.

The second part of this thesis, which comprises the main work of this thesis, concerns a port of the Linux IrDAstack to the SmartBadge. The IrDA-stack is a set of protocols that allow wireless communication between devices via an infrared link. These protocols are already widely used for data exchange between Laptops (and increasingly also PDAs), mobile phones and other mobile devices. Together with the use of Infrared-Access-Points this implementation provides wireless network-connectivity for the Badge. Through such wireless network access the possible range of applications again can be significantly extended. After an introduction to the relevant protocols I present the details of my implementation. I conclude with a summary of why fitting these various pieces of hardware and software together was difficult and provide some hints of future work. Abstract

## Acknowledgments

The work for this Master Thesis has been carried out in the Computer Communication Systems Laboratory (CCSlab) at the Department of Teleinformatics, Royal Institute of Technology (KTH) in Stockholm, Sweden during the period of February to July and October 2000.

I would like to express my sincerest gratitude to my advisor Prof. Gerald Q. Maguire Jr., head of the CCSlab, who guided me throughout the course of work for the thesis at hand. I deeply thank Prof. Maguire for his continuous and extraordinary support at work. Moreover, I would like to extend my thanks and appreciation for the many hours of interesting and instructive discussions, which widened my views and ways of thinking in many new aspects.

I would also like to thank my supervisor and examiner from the IAIK Graz, Dipl. Ing. Dr. Karl Christian Posch, for establishing the initial contact with Prof. Maguire.

Further thanks go to my friends and colleagues at the Teleinformatics Department, especially Enrico Pelletta, Iyad Al-Khatib and Pawel Wiatr, for their encouragements, patience, and continuous support by listening to my problems. Special thanks go to Alberto Escudero Pascal for his extensive help with all kinds of Linux related problems.

In addition, I would like to thank KTH's External Relations Office and the people from the ISS, the KTH Student Union Section for international students, for their efforts to make the exchange students' life in Stockholm easy, pleasant, and eventful.

Finally I would like to express my deepest thanks for the support and encouragement I have received from my family throughout my whole studies.

Acknowledgments

## **Table of Contents**

| Ab  | ostracti                                                                                                                                                                                          |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ac  | knowledgmentsiii                                                                                                                                                                                  |

| Та  | ble of Contentsv                                                                                                                                                                                  |

| Lis | st of Figuresix                                                                                                                                                                                   |

| Lis | st of Tables xi                                                                                                                                                                                   |

| Lis | stingsxiii                                                                                                                                                                                        |

| 1.  | Introduction1                                                                                                                                                                                     |

| 2.  | Basic Architectures 2                                                                                                                                                                             |

|     | 2.1 SmartBadge 3                                                                                                                                                                                  |

|     | 2.2 Description of the StrongARM SA-1100 Microcontroller                                                                                                                                          |

|     | 2.3 Peripheral Devices in the StrongARM Architecture                                                                                                                                              |

|     | 2.4 SmartBadge 4                                                                                                                                                                                  |

| 3.  | Operating Systems for the Badge11                                                                                                                                                                 |

|     | 3.1 Angel113.1.1 Introduction113.1.2 Angel C Library Support, Semihosted Operations123.1.3 Communications Architecture for Angel133.1.4 Serialization and CPU Modes143.1.5 Summary153.2 VxWorks15 |

|     | 3.3 E-Kernel                                                                                                                                                                                      |

| 4.  | Using some of the Peripherals16                                                                                                                                                                   |

|     | 4.1 Extensions to Angel                                                                                                                                                                           |

|     | 4.2 Support code                                                                                                                                                                                  |

|     | 4.3 Interrupts324.3.1 Register Description344.3.2 Interrupt handling under Angel364.3.3 Interrupt Controller Declarations and Functions364.3.4 Interrupt Latency under Angel41                    |

|    | 4.4 General Purpose I/O Controller (GPIO)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|    | <ul><li>4.4.1 Register Description</li><li>4.4.2 GPIO Declarations</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |

|    | 4.5 Peripheral Pin Controller (PPC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |

|    | 4.5.1 Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |

|    | <ul><li>4.5.2 PPC declarations</li><li>4.5.3 Maximum Toggling Frequency of GPIO and PPC Pins</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |

|    | 4.6 Real Time Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |

|    | 4.6.1 Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |

|    | 4.6.3 Real Time Clock Declarations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |

|    | 4.7 Operating System Timers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |

|    | 4.7.1 Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |

|    | 4.7.2 Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |

|    | <ul><li>4.7.3 OS Timer Declarations and Functions</li><li>4.7.4 Software Timer Implementation</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |

|    | 4.8 UARTs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

|    | <ul><li>4.8.1 Receive Operation</li><li>4.8.2 Transmit Operation</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |

|    | 4.8.3 FIFOs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |

|    | 4.8.4 Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |

|    | 4.8.5 UART Declarations and Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 79       |

| 5. | Infrared Communication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 86       |

|    | 5.1 Hardware Modifications to the SmartBadge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |

|    | 5.1.1 Modifications to Observe Communication via a Logic Analyzer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |

|    | 5.1.2 Modifications to Allow SIR Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 86       |

|    | <ul><li>5.1.2 Modifications to Allow SIR Mode</li><li>5.2 SIR Mode</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 86<br>88 |

|    | 5.1.2 Modifications to Allow SIR Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |

|    | <ul> <li>5.1.2 Modifications to Allow SIR Mode</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |

|    | <ul> <li>5.1.2 Modifications to Allow SIR Mode</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |

|    | <ul> <li>5.1.2 Modifications to Allow SIR Mode</li> <li>5.2 SIR Mode</li> <li>5.2.1 SIR Using Normal UART Operation on Revised SA-1100</li> <li>5.2.2 SIR via Software Modulation</li> <li>5.3 FIR Mode</li> <li>5.3.1 Infrared High-Speed Modulation</li> <li>5.3.2 HSSP Frame Format</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |

|    | <ul> <li>5.1.2 Modifications to Allow SIR Mode</li> <li>5.2 SIR Mode</li> <li>5.2.1 SIR Using Normal UART Operation on Revised SA-1100</li> <li>5.2.2 SIR via Software Modulation</li> <li>5.3 FIR Mode</li> <li>5.3.1 Infrared High-Speed Modulation</li> <li>5.3.2 HSSP Frame Format</li> <li>5.3.3 Baud Rate Generation</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |

|    | <ul> <li>5.1.2 Modifications to Allow SIR Mode</li> <li>5.2 SIR Mode</li> <li>5.2.1 SIR Using Normal UART Operation on Revised SA-1100</li> <li>5.2.2 SIR via Software Modulation</li> <li>5.3 FIR Mode</li> <li>5.3.1 Infrared High-Speed Modulation</li> <li>5.3.2 HSSP Frame Format</li> <li>5.3.3 Baud Rate Generation</li> <li>5.3.4 Receive Operation</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

|    | <ul> <li>5.1.2 Modifications to Allow SIR Mode</li> <li>5.2 SIR Mode</li> <li>5.2.1 SIR Using Normal UART Operation on Revised SA-1100</li> <li>5.2.2 SIR via Software Modulation</li> <li>5.3 FIR Mode</li> <li>5.3.1 Infrared High-Speed Modulation</li> <li>5.3.2 HSSP Frame Format</li> <li>5.3.3 Baud Rate Generation</li> <li>5.3.4 Receive Operation</li> <li>5.3.5 Transmit Operation</li> <li>5.3.6 Transmit and Receive FIFOs</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |

|    | <ul> <li>5.1.2 Modifications to Allow SIR Mode</li> <li>5.2 SIR Mode</li> <li>5.2.1 SIR Using Normal UART Operation on Revised SA-1100</li> <li>5.2.2 SIR via Software Modulation</li> <li>5.3 FIR Mode</li> <li>5.3.1 Infrared High-Speed Modulation</li> <li>5.3.2 HSSP Frame Format</li> <li>5.3.3 Baud Rate Generation</li> <li>5.3.4 Receive Operation</li> <li>5.3.5 Transmit Operation</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |

|    | <ul> <li>5.1.2 Modifications to Allow SIR Mode</li> <li>5.2 SIR Mode</li> <li>5.2.1 SIR Using Normal UART Operation on Revised SA-1100</li> <li>5.2.2 SIR via Software Modulation</li> <li>5.3 FIR Mode</li> <li>5.3.1 Infrared High-Speed Modulation</li> <li>5.3.2 HSSP Frame Format</li> <li>5.3.3 Baud Rate Generation</li> <li>5.3.4 Receive Operation</li> <li>5.3.5 Transmit Operation</li> <li>5.3.6 Transmit and Receive FIFOs</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |

|    | <ul> <li>5.1.2 Modifications to Allow SIR Mode</li> <li>5.2 SIR Mode</li> <li>5.2.1 SIR Using Normal UART Operation on Revised SA-1100</li> <li>5.2.2 SIR via Software Modulation</li> <li>5.3 FIR Mode</li> <li>5.3.1 Infrared High-Speed Modulation</li> <li>5.3.2 HSSP Frame Format</li> <li>5.3.3 Baud Rate Generation</li> <li>5.3.4 Receive Operation</li> <li>5.3.5 Transmit Operation</li> <li>5.3.6 Transmit and Receive FIFOs</li> <li>5.3.7 HSSP Register Description</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                           |          |

| 6. | <ul> <li>5.1.2 Modifications to Allow SIR Mode</li> <li>5.2 SIR Mode</li> <li>5.2.1 SIR Using Normal UART Operation on Revised SA-1100</li> <li>5.2.2 SIR via Software Modulation</li> <li>5.3 FIR Mode</li> <li>5.3.1 Infrared High-Speed Modulation</li> <li>5.3.2 HSSP Frame Format</li> <li>5.3.3 Baud Rate Generation</li> <li>5.3.4 Receive Operation</li> <li>5.3.5 Transmit Operation</li> <li>5.3.6 Transmit and Receive FIFOs</li> <li>5.3.7 HSSP Register Description</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                           |          |

| 6. | <ul> <li>5.1.2 Modifications to Allow SIR Mode</li> <li>5.2 SIR Mode</li> <li>5.2 SIR Mode</li> <li>5.2.1 SIR Using Normal UART Operation on Revised SA-1100</li> <li>5.2.2 SIR via Software Modulation</li> <li>5.3 FIR Mode</li> <li>5.3 FIR Mode</li> <li>5.3 Infrared High-Speed Modulation</li> <li>5.3.2 HSSP Frame Format</li> <li>5.3.3 Baud Rate Generation</li> <li>5.3.4 Receive Operation</li> <li>5.3.5 Transmit Operation</li> <li>5.3.6 Transmit and Receive FIFOs</li> <li>5.3.7 HSSP Register Description</li> </ul> 5.4 Support Code for Infrared Communication 5.5 Setup to Debug Infrared Communication 6.1 Methods of Accessing the Peripherals' Registers.                                                                                                                                                                                                      |          |

| 6. | <ul> <li>5.1.2 Modifications to Allow SIR Mode</li> <li>5.2 SIR Mode</li> <li>5.2.1 SIR Using Normal UART Operation on Revised SA-1100</li> <li>5.2.2 SIR via Software Modulation</li> <li>5.3 FIR Mode</li> <li>5.3.1 Infrared High-Speed Modulation</li> <li>5.3.2 HSSP Frame Format</li> <li>5.3.3 Baud Rate Generation</li> <li>5.3.4 Receive Operation</li> <li>5.3.5 Transmit Operation</li> <li>5.3.6 Transmit and Receive FIFOs</li> <li>5.3.7 HSSP Register Description</li> </ul> 5.4 Support Code for Infrared Communication 5.5 Setup to Debug Infrared Communication 6.1 Methods of Accessing the Peripherals' Registers <ul> <li>6.1.1 Declaration as const unsigned int</li> </ul>                                                                                                                                                                                     |          |

| 6. | <ul> <li>5.1.2 Modifications to Allow SIR Mode</li> <li>5.2 SIR Mode</li> <li>5.2.1 SIR Using Normal UART Operation on Revised SA-1100</li> <li>5.2.2 SIR via Software Modulation</li> <li>5.3 FIR Mode</li> <li>5.3.1 Infrared High-Speed Modulation</li> <li>5.3.2 HSSP Frame Format</li> <li>5.3.3 Baud Rate Generation</li> <li>5.3.4 Receive Operation</li> <li>5.3.5 Transmit Operation</li> <li>5.3.6 Transmit and Receive FIFOs</li> <li>5.3.7 HSSP Register Description</li> </ul> 5.4 Support Code for Infrared Communication 5.5 Setup to Debug Infrared Communication 6.1 Methods of Accessing the Peripherals' Registers <ul> <li>6.1 Methods of Accessing the Peripherals' Registers</li> <li>6.1.1 Declaration as const unsigned int</li> <li>6.1.2 Declaration as Pointer</li> </ul>                                                                                  |          |

| 6. | <ul> <li>5.1.2 Modifications to Allow SIR Mode</li> <li>5.2 SIR Mode</li> <li>5.2 SIR Using Normal UART Operation on Revised SA-1100</li> <li>5.2.2 SIR via Software Modulation</li> <li>5.3 FIR Mode</li> <li>5.3.1 Infrared High-Speed Modulation</li> <li>5.3.2 HSSP Frame Format</li> <li>5.3.3 Baud Rate Generation</li> <li>5.3.4 Receive Operation</li> <li>5.3.5 Transmit Operation</li> <li>5.3.6 Transmit and Receive FIFOs</li> <li>5.3.7 HSSP Register Description</li> </ul> 5.4 Support Code for Infrared Communication 5.5 Setup to Debug Infrared Communication 6.1 Methods of Accessing the Peripherals' Registers <ul> <li>6.1.1 Declaration as const unsigned int</li> <li>6.1.2 Declaration as Structure</li> </ul>                                                                                                                                               |          |

| 6. | <ul> <li>5.1.2 Modifications to Allow SIR Mode</li> <li>5.2 SIR Mode</li> <li>5.2.1 SIR Using Normal UART Operation on Revised SA-1100</li> <li>5.2.2 SIR via Software Modulation</li> <li>5.3 FIR Mode</li> <li>5.3.1 Infrared High-Speed Modulation</li> <li>5.3.2 HSSP Frame Format</li> <li>5.3.3 Baud Rate Generation</li> <li>5.3.4 Receive Operation</li> <li>5.3.5 Transmit Operation</li> <li>5.3.6 Transmit and Receive FIFOs</li> <li>5.3.7 HSSP Register Description</li> <li>5.4 Support Code for Infrared Communication</li> <li>5.5 Setup to Debug Infrared Communication</li> <li>5.6 Setup to Debug Infrared Communication</li> <li>6.1 Methods of Accessing the Peripherals' Registers</li> <li>6.1.1 Declaration as const unsigned int</li> <li>6.1.2 Declaration as Structure</li> <li>6.1.4 Use of #define</li> <li>6.2.1 ARM load/store Instructions</li> </ul> |          |

| 6. | <ul> <li>5.1.2 Modifications to Allow SIR Mode</li> <li>5.2 SIR Mode</li> <li>5.2 SIR Using Normal UART Operation on Revised SA-1100</li> <li>5.2.2 SIR via Software Modulation</li> <li>5.3 FIR Mode</li> <li>5.3.1 Infrared High-Speed Modulation</li> <li>5.3.2 HSSP Frame Format</li> <li>5.3.3 Baud Rate Generation</li> <li>5.3.4 Receive Operation</li> <li>5.3.5 Transmit Operation</li> <li>5.3.6 Transmit and Receive FIFOs</li> <li>5.3.7 HSSP Register Description</li> </ul> 5.4 Support Code for Infrared Communication 5.5 Setup to Debug Infrared Communication 6.1 Methods of Accessing the Peripherals' Registers <ul> <li>6.1.1 Declaration as const unsigned int</li> <li>6.1.2 Declaration as Structure</li> <li>6.1.4 Use of #define</li> </ul>                                                                                                                 |          |

#### **Table of Contents**

| Appen | dix A. Infrared support code                                                                                                                                                                                                                                                   |  |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| A.1   | The Header File, Containing Constants and Macros                                                                                                                                                                                                                               |  |

| A.2   | Implementation of the SIR-Functions                                                                                                                                                                                                                                            |  |

|       | Implementation of the FIR-Functions                                                                                                                                                                                                                                            |  |

|       | dix B. Example Programs                                                                                                                                                                                                                                                        |  |

| B.1   | GPIO and PPC - Maximum Frequency Pin Toggling<br>B.1.1 Standalone Version<br>B.1.2 Angel Version                                                                                                                                                                               |  |

| B.2   | GPIO - Interrupt Latency                                                                                                                                                                                                                                                       |  |

| B.3   | Real Time Clock Example                                                                                                                                                                                                                                                        |  |

| B.4   | OS Timer Examples<br>B.4.1 Basic Use of the Macros - Timer Controlled Pin Toggling<br>B.4.2 Use of the Software Timer Functions                                                                                                                                                |  |

| B.5   | Serial Communication Example (UART)<br>B.5.1 Echo                                                                                                                                                                                                                              |  |

| B.6   | IR SIR-Mode Examples<br>B.6.1 SIR Receiver in Polled Mode<br>B.6.2 SIR Receiver in Interrupt Mode<br>B.6.3 SIR Transmitter Using UART2 in Polled Mode<br>B.6.4 SIR Transmitter Using UART2 in Interrupt Mode<br>B.6.5 SIR Operation Using Software Modulation for Transmission |  |

| B.7   | IR FIR-Mode Examples<br>B.7.1 FIR Receiver in Polled Mode<br>B.7.2 FIR Transmitter in Polled Mode                                                                                                                                                                              |  |

| Appen | dix C. IrDA                                                                                                                                                                                                                                                                    |  |

| C.1   | Implementation of irport.c                                                                                                                                                                                                                                                     |  |

|       | Implementation of wrapper.h                                                                                                                                                                                                                                                    |  |

| C.3   | Implementation of wrapper.c                                                                                                                                                                                                                                                    |  |

|       | Debug Log Connection Establishment                                                                                                                                                                                                                                             |  |

## **List of Figures**

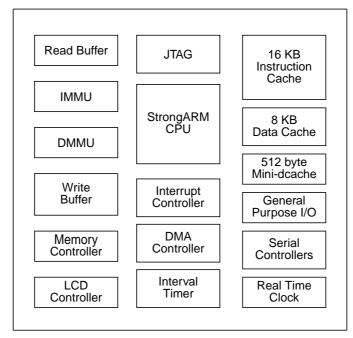

| Figure 1.  | SmartBadge 3 Block Diagram                                          | 2   |

|------------|---------------------------------------------------------------------|-----|

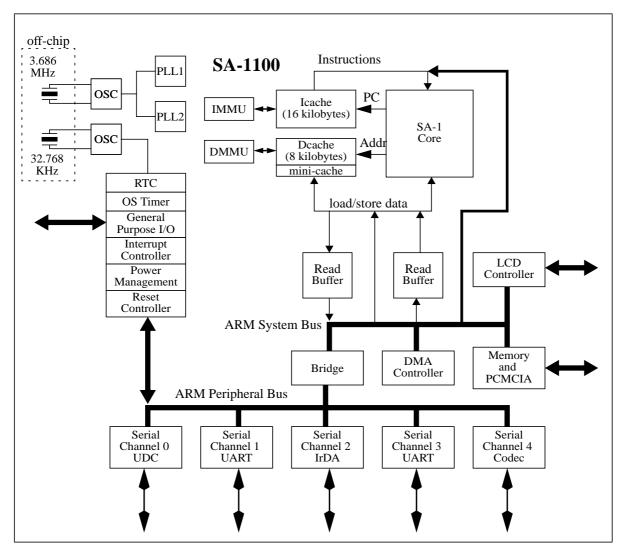

| Figure 2.  | Components of the StrongARM SA-1100                                 | 5   |

| Figure 3.  | SA-1100 Block Diagram (Note that the two crystals are off-chip)     | 8   |

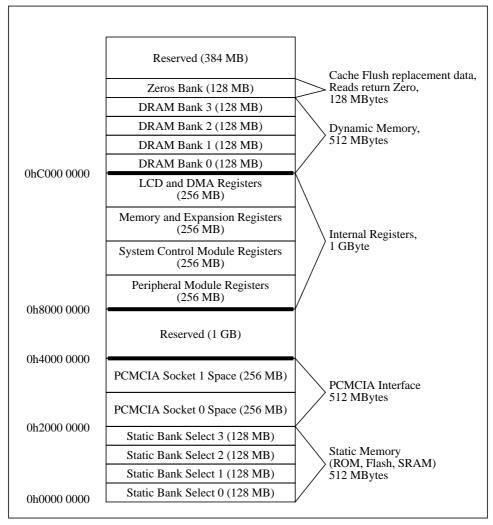

| Figure 4.  | SA-1100 Memory Map                                                  | 9   |

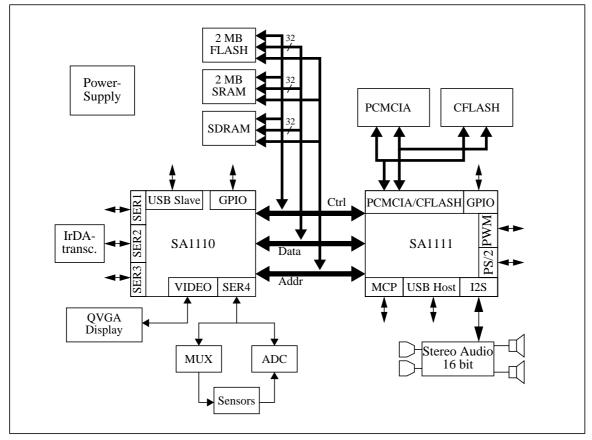

| Figure 5.  | SmartBadge 4 Block Diagram                                          | 10  |

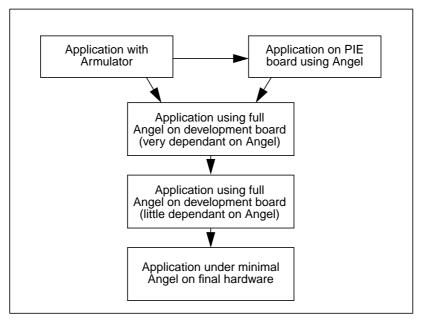

| Figure 6.  | The Angel development cycle [4, p. 6-4]                             |     |

| Figure 7.  | Communication layers for Angel [3, p. 8-10]                         |     |

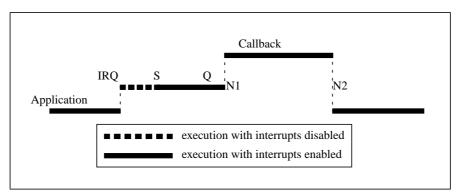

| Figure 8.  | Serialization [3, p. 8-38]                                          | 14  |

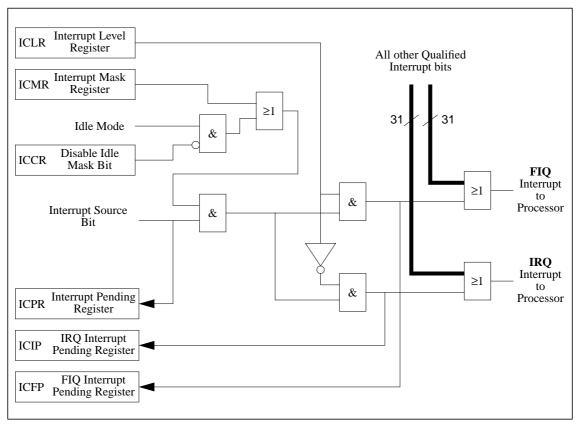

| Figure 9.  | Interrupt Controller Block Diagram                                  |     |

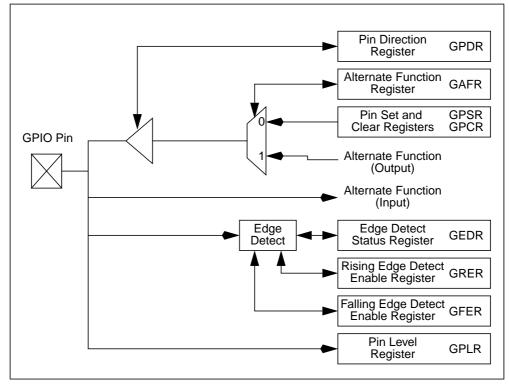

| Figure 10. | GPIO port block diagram.                                            |     |

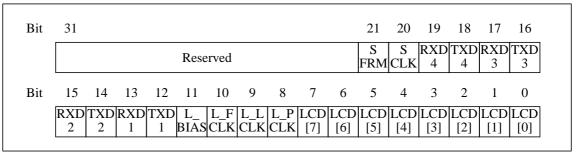

| Figure 11. | PPC Pin Direction Register                                          | 47  |

| Figure 12. | PPC Pin Flag Register                                               | 49  |

| Figure 13. | RTC Status Register (RTSR)                                          | 53  |

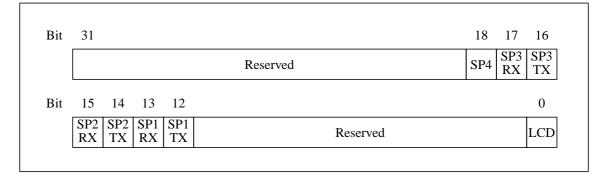

| Figure 14. | UART Data Frame                                                     | 72  |

| Figure 15. | Example for NRZ encoding                                            | 73  |

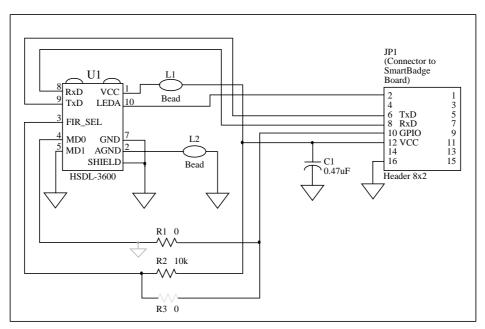

| Figure 16. | IR daughtercard circuit diagram (default configuration)             | 87  |

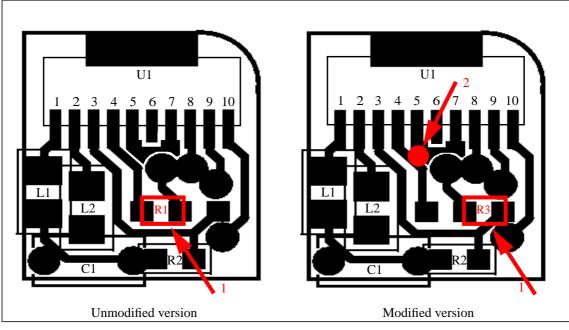

| Figure 17. | IR Daughtercard Modification                                        |     |

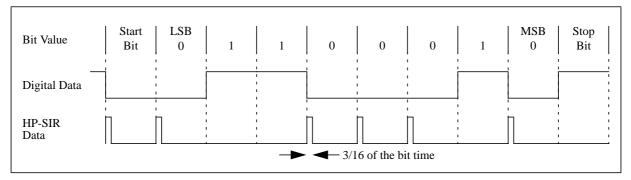

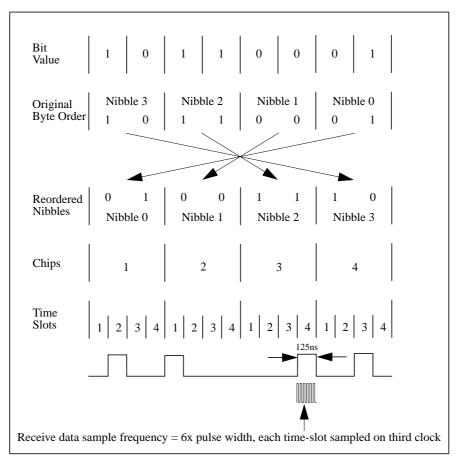

| Figure 18. | HP-SIR Modulation Example                                           |     |

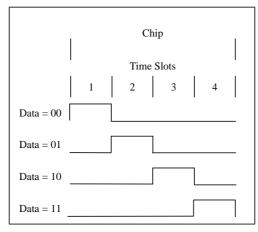

| Figure 19. | 4PPM Modulation Encoding                                            |     |

| Figure 20. | 4PPM Modulation example                                             |     |

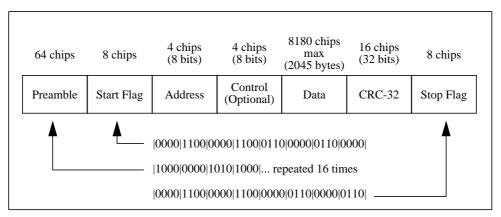

| Figure 21. | High Speed Serial Frame Format for IrDA Transmission (4.0Mbps)      |     |

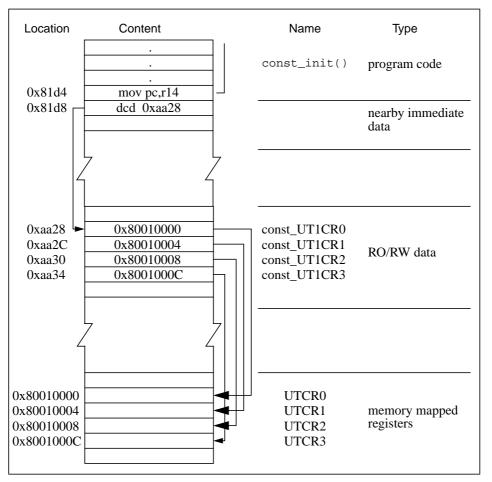

| Figure 22. | Memory layout for const/pointer variant                             | 108 |

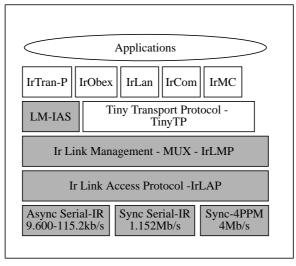

| Figure 23. | IrDA protocol stack [16]                                            |     |

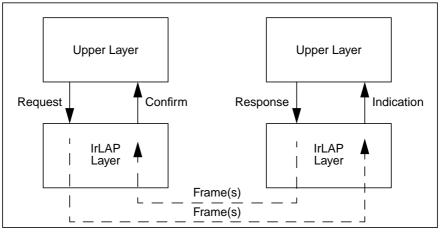

| Figure 24. | IrDA Service Primitives [12, p. 14]                                 | 133 |

| Figure 25. | IrLAP frame format [12, p. 21]                                      |     |

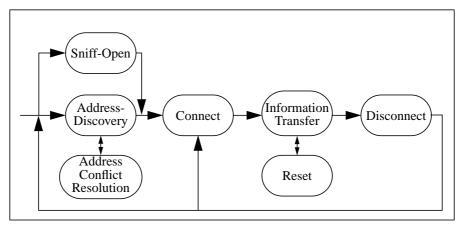

| Figure 26. | IrLAP state diagram [12, p. 34]                                     |     |

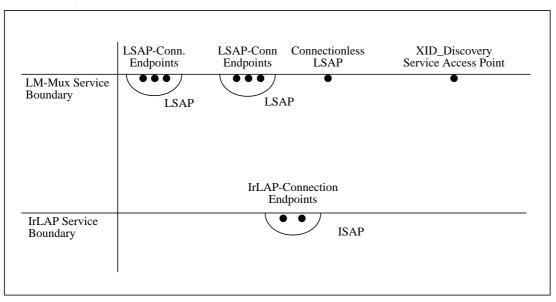

| Figure 27. | LM-MUX External Interfaces [13, p. 17]                              | 136 |

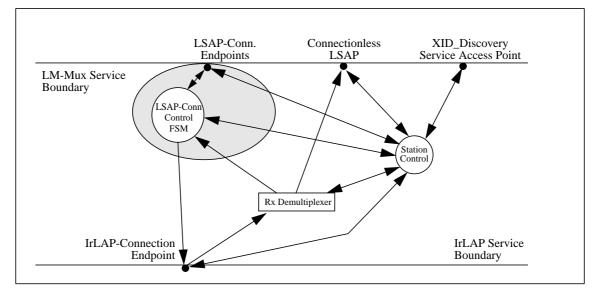

| Figure 28. | Internal Multiplexer Organization [13, p.19]                        | 137 |

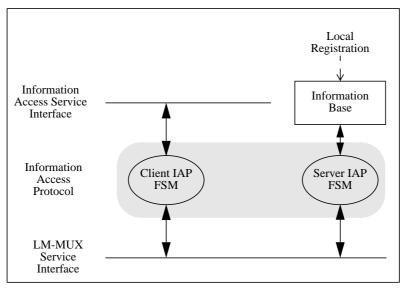

| Figure 29. | Internal Organization of the Information Access Service [13, p. 67] | 138 |

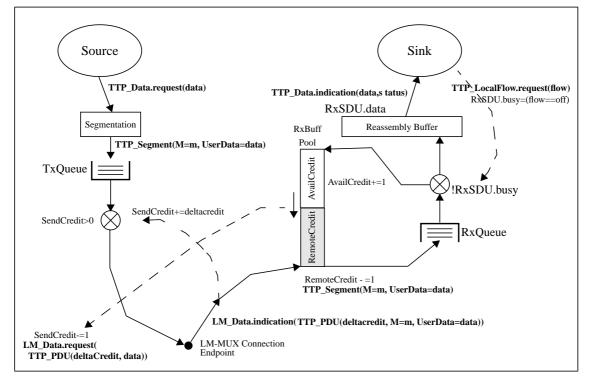

| Figure 30. | Tiny TP SAR and Credit Flow [14, p. 9]                              | 140 |

List of Figures

## List of Tables

| Table 1.  | Data cache operation                                           | 7   |

|-----------|----------------------------------------------------------------|-----|

| Table 2.  | Exception vector table                                         | 33  |

| Table 3.  | Interrupt Controller register block                            | 34  |

| Table 4.  | Bits in the Interrupt Controller registers                     | 34  |

| Table 5.  | Interrupt latency depending on various cache and build options | 41  |

| Table 6.  | GPIO register block                                            | 43  |

| Table 7.  | PPC register block                                             | 47  |

| Table 8.  | Maximum toggling of GPIO and PPC pins [high time/period time]  | 51  |

| Table 9.  | Real Time Clock register block                                 | 52  |

| Table 10. | OS Timer register block                                        | 57  |

| Table 11. | Base addresses for SA-1100 UARTs 1, 2, and 3                   | 74  |

| Table 12. | UART register block                                            | 74  |

| Table 13. | UART Control Register 0                                        | 75  |

| Table 14. | UART Control Register 3                                        | 76  |

| Table 15. | UART Status Register 0                                         | 77  |

| Table 16. | UART Status Register 1                                         | 78  |

| Table 17. | HSDL-3600 Transceiver Control Truth Table                      | 87  |

| Table 18. | HSSP register block                                            | 96  |

| Table 19. | HSSP Control Register                                          | 96  |

| Table 20. | HSSP Status Register 0 (HSSR0)                                 | 99  |

| Table 21. | HSSP Status Register 1 (HSSR1)                                 | 100 |

| Table 22. | Memory map                                                     | 113 |

| Table 23. | Number of instructions for first register access               | 114 |

| Table 24. | Number of instructions for subsequent register accesses        |     |

| Table 25. | IrLAN Commands [15, p. 16]                                     | 142 |

List of Tables

## Listings

| Listing 1.  | General support declarations and macros [file util/util_misc.h]              |

|-------------|------------------------------------------------------------------------------|

| Listing 2.  | General support functions and macros [file util_misc.c]                      |

| Listing 3.  | Generic interrupt declarations and macros [file util_util_interrupt.h]       |

| Listing 4.  | Code to deal with interrupts under Angel [file util_interrupt.c]             |

| Listing 5.  | GPIO declarations and macros [file util/util_gpio.h]                         |

| Listing 5.  | PPC declarations and macros [file util\util_ppc.h]                           |

| -           | Real Time Clock declarations and Macros [file util\util\realtime.h]          |

| Listing 7.  |                                                                              |

| Listing 8.  | OS Timer declarations and macros [file util_util_ostimer.h]                  |

| Listing 9.  | Functions to use the OS Timer functionality [file util_ostimer.c]            |

| Listing 10. | Declarations for the software timer functionality [file util\util_ostimer.h] |

| Listing 11. | Functions for SW timers and bottom half handling                             |

| Listing 12. | UART macros and declarations [file util\util_serial.h]                       |

| Listing 13. | Functions to use the UARTs [file util_serial.c]                              |

| Listing 14. | Register access with const unsigned int                                      |

| Listing 15. | Register access with pointers                                                |

| Listing 16. | Register access using a structure                                            |

| Listing 17. | Register access using #define                                                |

| Listing 18. | Code for const declaration without optimisations107                          |

| Listing 19. | Code for pointer to struct without optimisations                             |

| Listing 20. | Code for #define without optimisations    109                                |

| Listing 21. | Code for const declaration with "no register allocation"                     |

| Listing 22. | Code for struct declaration with "no register allocation"                    |

| Listing 23. | Code for define declaration with "no register allocation"                    |

| Listing 24. | Optimal code for the UART init function                                      |

| Listing 25. | Code for const declaration with full optimisation                            |

| Listing 26. | Read a character from a serial port in polling mode                          |

| Listing 27. | Erroneous code                                                               |

| Listing 28. | Correct code using volatile                                                  |

| Listing 29. | Direct debug output via a serial port                                        |

| Listing 30. | Ring buffer declarations [file util\util_ringbuf.h]119                       |

| Listing 31. | Ring buffer functions [file util_ringbuf.c]                                  |

| Listing 32. | Debug declarations and inline functions [util\util_debug.h]                  |

| Listing 33. | Debug functions [util_debug.c]                                               |

| Listing 34. | Defines to be put in files to support debug output                           |

| Listing 35. | UDP echo server on the Badge                                                 |

| Listing 36. | IP stack initialization code                                                 |

| Listing 37. | Constants, macros and function prototypes for IR on the SmartBadge           |

| Listing 38. | Implementation of SIR-related functions                                      |

| Listing 39. | Implementation of FIR-related functions                                      |

| Listing 40. | GPIO/PPC pin toggling, standalone version                                    |

| Listing 41. | GPIO/PPC pin toggling, Angel version                                         |

| Listing 42. | GPIO interrupts                                                              |

| Listing 43. | Realtime clock                                                               |

| Listing 44. | Timer controlled pin toggling                                                |

| Listing 45. | Software timers                                                              |

| Listing 45. | Basic echo program                                                           |

| Listing 40. | SIR-receiver in polled mode                                                  |

| U           | SIR-receiver in poned mode                                                   |

| Listing 48. | •                                                                            |

| Listing 49. | SIR-transmitter using the SA-1100 UART in polled mode                        |

| Listing 50. | SIR-transmitter using the SA-1100 UART in interrupt mode                     |

| Listing 51. | SIR-transmitter using software modulation                                    |

| Listing 52. | FIR-receiver in polled mode                                                  |

| Listing 53. | FIR-transmitter in polled mode        | 206   |

|-------------|---------------------------------------|-------|

| Listing 54. | Listing of irport.c                   | . 208 |

| Listing 55. | Listing of wrapper.h.                 | . 222 |

| Listing 56. | Listing of wrapper.c                  | . 223 |

| Listing 57. | Debug log of connection establishment | . 229 |

## **1. Introduction**

With ever growing computing power and increasing levels of integration which leads to the ever decreasing size and price of electronic components -- mobile applications are increasingly important. PDAs already offer impressive computing power and mobile phones are a fixture of everyday's life. Increasingly these advances are leading to a fusion of PDA like devices with communication. This is compounded with the explosive growth of the internet.

Prof. Gerald Maguire, head of the Computer Communication Systems Laboratory (CCSlab) at the Department of Teleinformatics, KTH, Stockholm, Sweden and Dr. Mark. T. Smith, HP Labs, Palo Alto, California, USA have developed a wearable computing platform that was optimized in terms of power consumption and size, but yet offers state of the art computing power. In addition to that they have integrated a number of sensors for measuring light, temperature, humidity, and acceleration. This allows one to investigate and develop a new class of applications and services. The new concept is that the applications now can acquire information about their environment. This results in so called context- and location-aware services. Some location aware services have already been introduced, for example mobile systems that detect their location (e.g. by means of the global positioning system (GPS) or by other means provided by the cellular network infrastructure) and based upon the knowledge of their position can offer information services that provide (only) information that is relevant at a certain location (this could be information about shops, restaurants, public services, localized traffic information and many more).

The sensors also add an additional dimension. They can detect if the device is still attached to its user (which could be used for authentication mechanisms). As long as the users are still wearing their device they do not need to reauthenticate. Other applications are e.g. medical monitoring. Combining these additional technologies and a communication infrastructure allows services that are based on both the location and the context of a user.

In addition these so called SmartBadges are equipped with audio input and output, an IR transceiver, and can utilize PCMCIA-form factor network adapters (the later two can provide wireless access to network infrastructure). All this put together results in a huge field of possible applications.

The SmartBadge as used in this thesis was version 3, a new version 4 is to be introduced soon. In the course of this thesis work my main field of work involved enabling infrared communication, with the final goal to provide network access via an infrared link.

After a short introduction to the hardware platform and the available operating systems I present the use of some of the processor units such as: serial communication, general purpose Input/Output, timers, etc. Later chapters describe some aspects of the code generation of the compiler and the problems of debugging embedded systems. The final chapters present the main result of my work, an implementation of the IrDA protocol stack which in combination with an infrared access point (that is attached to a fixed network) provides the SmartBadge with network access via an infrared link.

## 2. Basic Architectures

In this chapter I give an introduction to the hardware architectures of both SmartBadge 3 and the new SmartBadge 4. As most of my work was based on SmartBadge 3, I also give a short overview of the StrongARM SA-1100 microcontroller which is used on Badge 3. Its successor, the SA-1110, used on Badge 4, differs from the SA-1100 only in the memory interface (which now also supports SDRAM and allows SRAM, DRAM, and SDRAM in the same system) and the PCMCIA controller. The SA-1111 companion chip provides the PCMCIA controller as well as support for Compact Flash, a complete USB Host Controller, two serial ports (Serial Audio Controller and SSP Serial Port), PS/2 Trackpad and Mouse Interfaces and an additional general purpose I/O Interface.

### 2.1 SmartBadge 3

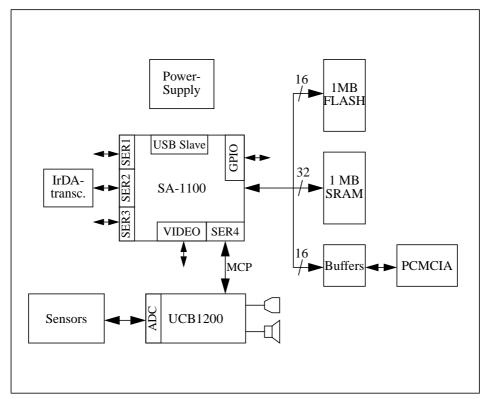

SmartBadge 3 [1] consists of the following basic blocks as shown in Figure 1:

Figure 1. SmartBadge 3 Block Diagram

The central element is an Intel StrongARM SA-1100, a 32 bit RISC controller clocked at up to 200MHz. It is connected to 1 MB of FLASH memory (16 bit), 1 MB of SRAM (32 bit) and an audio and telecom codec (Philips UCB 1200). The SA-1100 is described in more detail in the next section.

The circuit can be powered by onboard batteries or - for test and development - by an external power supply. The power supply block takes this unstabilized voltage and generates 1.5V for the microcontroller core, 3.3 V for the microcontroller peripherals and the other circuits and optionally 5V for the PCMCIA slot if a 5V card is used. The buffers between the SA-1100 and the PCMCIA connector are necessary to convert between the 3.3 V system supply and the 5V PCMCIA supply, when a 5V card is being used.

The FLASH memory is 16 bit wide while the SRAM memory utilizes the full width of 32 bit. Although the SA-1100 also supports DRAM, SmartBadge 3 doesn't provide any DRAM, mainly to reduce the power consumption.

The Philips UCB1200 [2] is a single chip, integrated mixed signal audio and telecom codec. It allows direct connection of a microphone and a speaker via the audio codec channel. The telecom codec channel can be directly connected to a DAA and supports high speed modem protocols. These two channels mainly differ in the output impedance, therefore if the telecom functionality is not required the two channels can be combined to form stereo audio input/output. In addition the UCB contains a built-in 10-bit ADC. A built-in analog multiplexer allows selection between four general purpose analog inputs and a four input touch screen interface. Finally there are ten digital general purpose I/O-pins available. On SmartBadge 3 the general purpose ADC-inputs and two of the touch screen interface inputs are used to read in the analog sensor values while the digital I/O-pins allow selectively powering the sensors. The UCB1200 is connected to the SA-1100 via the multimedia serial port (serial port 4, MSP mode).

The following sensors are included by default, additional sensors can be connected via the general purpose I/O-pins or the serial ports, if required:

- three-axis accelerometer,

- two humidity sensors,

- two temperature sensors,

- a light sensor.

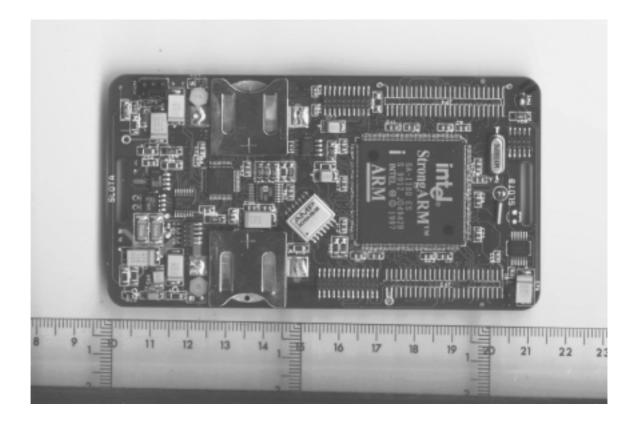

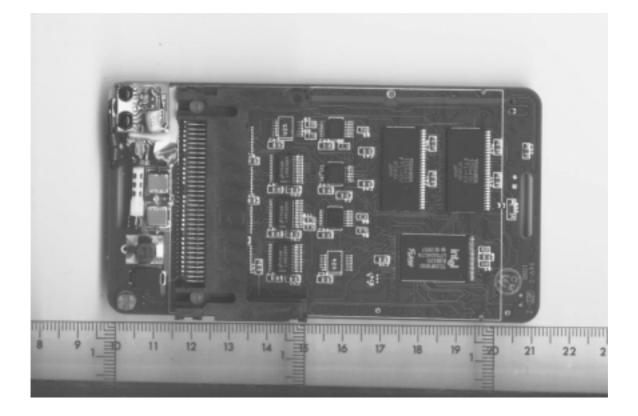

The light sensor is mounted on the front side, as well as one of the humidity sensors and one of the temperature sensors. The other sensors are mounted on the backside. This allows the system to differentiate between sensors on the side orientated towards the user's body and the side orientated away from the body if the Badge is worn, using one of the two slots in the Badge - as shown in the two photos below:

### 2.2 Description of the StrongARM SA-1100 Microcontroller

The StrongARM SA-1100 [6] is a highly integrated high-performance low-power microcontroller, especially suited for (mobile) telecommunication applications. It consists of a 32-bit StrongARM RISC processor core, extended by system support logic (memory-, DMA-, interrupt-, power-management-controllers, timers and real-time-clock), caches, various communication-channels, an LCD controller, PCMCIA controller, and general purpose input/output ports. Due to its special low-power design it has a typical power dissipation of about 200 mW @ 200 MHz. For further power saving the clock can be slowed or stopped under software control. Logically these elements can be grouped into the following main modules:

- Processor core

- MMU, caches, read and write buffer

- System Control Module (General Purpose I/O, Interrupt Controller, Real Time Clock, Operating System Timer, Power Manager, Reset Controller)

- Memory and PCMCIA Control Module

- Peripheral Control Module (DMA Controller, LCD Controller, Serial Ports 0-4, Peripheral Pin Controller)

Figure 2. Components of the StrongARM SA-1100

In the following sections I will give a short overview of the caches, buffers and MMU. More detailed information can be found in [5] and [6]. Some of the peripheral units will be described in more detail in a later chapter (See 4. "Using some of the Peripherals").

#### 2.2.1 Instruction Cache

The instruction cache (IC) has a size of 16 kBytes, set up as 512 lines of 32 bytes (8 words) and is arranged as a 32 way set associative cache. It can be enabled or disabled via the SA-1100 Control Register and is disabled through a reset sequence (i.e. on the assertion of the nRESET line, software or sleep). It's operation further depends on the state of the Memory Management Unit and the Cacheable bit stored in the Memory Management Page Table. The cache works as follows:

The IC operates with virtual addresses, therefore care must be taken to ensure consistency with the MMU mappings, special care is needed if the mappings are changed. The IC is not coherent with stores to memory. If a program writes to cacheable instruction locations not only must the cache operation be taken into consideration but also the write buffer (see section 2.2.3) must be drained as instruction fetches do not check the write buffer.

If the cache is disabled, no lines are placed in the cache, but the cache is always searched and data found will be used by the processor - only cache misses are affected by the state of the cache, the MMU and the Cacheable (C) bit. This is particularly important if the cache is disabled by software after having been enabled for some time. If the data in the cache must not be used the cache must be flushed.

In the case of a cache miss the behaviour depends on the state of the MMU and the Cacheable bit:

- MMU disabled or C bit is set for the given virtual address: a linefetch of eight words is performed and placed in a cache bank with a round-robin replacement algorithm.

- MMU enabled and C bit is zero for the given virtual address: an external memory access for a single word is performed and the cache is not written.

Note: if Memory Management is disabled, all addresses are regarded as cacheable (i.e. C=1).

#### 2.2.2 Data Caches

The SA-1100 contains two logically separate data caches:

- · main data cache: intended for use during most data accesses

- mini data cache (also called mini-cache): alternate caching structure for dealing with large data structures which could thrash the main cache.

Both caches use virtual addresses and allocate only on loads, write misses never allocate in the cache. Besides the actual data each cache line contains also the physical address of this line and two dirty bits. The dirty bits indicate the status of the first and the second half of the line. Store hits in the cache cause the associated dirty bit to be set. When a line is evicted from the cache the dirty bits are used to decide which part of the line (all, half, or none) has to be written back to memory using the physical address stored together with the line. Both caches always reload a complete line (8 words) at a time.

As for the instruction cache the data caches can be enabled and disabled via the SA-1100 Control Register and are disabled by resets (including watchdog reset). Apart from this global enabling/disabling the operation depends on the Bufferable (B) bit and the Cacheable (C) bit stored in the Memory Management Page Table. Cache operation therefore requires the MMU to be enabled. Again as virtual addresses are used by the caches consistency in the virtual to physical mappings performed by the MMU must be ensured. In particular it is assumed that every virtual address maps to a different physical address. Doubly-mapped virtual addresses should be marked as uncacheable to avoid cache inconsistencies (each virtual address has a separate entry in the cache and only one entry is updated on a write operation).

Typically main memory is marked as cacheable whereas I/O space should always be marked as uncacheable to make sure that the hardware registers are always directly read instead of copies of earlier values stored in the cache.

#### 2.2.2.1 Main Data Cache

The main data cache is an 8 kByte writeback data cache. It consists of 256 lines of 32 bytes (8 words) in a 32 way set associative organization (i.e. 8 sets, each consisting of 32 blocks of 8 words). It allocates on loads to memory locations marked as B=1 and C=1. Replacements in the main data cache are selected according to a set of round robin pointers. At reset the pointers in each set of the cache point to block zero of each 32-block set. As lines are allocated, the pointers are incremented to the next block. After block 31 has been allocated, the next line fill replaces (and copies back to memory, if dirty) the data in block zero.

#### 2.2.2.2 Mini Data Cache

The mini-cache is a 512 byte writeback cache consisting of 16 lines of 32 bytes (8 words) in a 2 way set associative organization. It allocates on loads to memory locations marked as B=0 and C=1. Replacements in the mini data cache also use a round robin pointer mechanism. But, since this cache is only two way set associative, the replacement algorithm reduces to a simple Least-Recently-Used (LRU) mechanism.

#### 2.2.2.3 Detailed Operation with Respect to the C and B Bits

Cache hits are always served, i.e. on a load cache hit the according cache delivers the data and on a store cache hit the data is stored to the according cache and the line is marked as dirty.

As the caches only allocate on load misses, on a store miss the data is stored to memory without affecting the cache (no allocation).

In the case of a load cache miss the operation depends on the C and B bits as follows:

- C=0: load from memory, no cache allocation

- C=1 and B=0: load from memory and allocate to mini cache

- C=1 and B=1: load from memory and allocate to main cache

|   |   |                    | load                   |                         | store                        |

|---|---|--------------------|------------------------|-------------------------|------------------------------|

| В | С | cache hit          | cache miss             | cache hit               | cache miss                   |

| 0 | 0 | deliver cache data | load from memory -     | store to either cache - | store to memory, no allocate |

|   |   |                    | no allocate            | mark line dirty         |                              |

| 0 | 1 | deliver cache data | allocate to mini cache | store to either cache - | store to memory, no allocate |

|   |   |                    |                        | mark line dirty         |                              |

| 1 | 0 | deliver cache data | load from memory -     | store to either cache - | store to memory, no allocate |

|   |   |                    | no allocate            | mark line dirty         |                              |

| 1 | 1 | deliver cache data | allocate to main cache | store to either cache - | store to memory, no allocate |

|   |   |                    |                        | mark line dirty         |                              |

Table 1. Data cache operation

#### 2.2.2.4 Data Cache Flush

The SA-1100 supports flush and clean operations on single entries of the data caches as well as flushing the whole cache by writes to the Cache Operations registers. But as the caches are writeback caches, in order to prevent the loss of data, a flush whole must be preceded by a sequence of loads to cause the cache to write back any dirty entries. The memory controller in the SA-1100 provides an internally decoded memory space (residing in the upper 512 Megabytes of the memory map, starting at virtual address 0xE000 0000) that returns zeros without incurring external memory latency.

#### 2.2.3 Write Buffer

The SA-1100 contains a write buffer to improve system performance by buffering up to eight blocks of data of 1 to 16 bytes at independent addresses. The buffer can be globally enabled or disabled via the SA-1100 Control Register. Its operation further depends on the Cacheable and Bufferable bits in the Memory Management Page Tables, therefore the MMU must be enabled in order to use the write buffer.

In detail it operates as follows:

When the CPU performs a store, first the data caches are checked. If the store hits in one of the caches the write completes in the cache, provided that the protection for the location and the mode of the store allow the write to the cache. The write buffer is not used.