This is an example design description generated using the EDDA documentation system.

The example is a simple MOS gain stage.

The circuit consists of an AC coupled common source stage. The circuit is biased using a current mirror.

The 3dB cutoff frequency of the circuit can be calculated using equation (1):

| (1) |

The simulation results are summarised in table 1.

| Parameter | Spec | Result | Unit | Pass | ||||

|---|---|---|---|---|---|---|---|---|

| Min | Typ | Max | Min | Typ | Max | |||

| AC simulation | ||||||||

| AC gain | 17 | 25 | 19.7 (slow) | 20.5 | 21.9 (fast) | dB | ||

| 3dB Bandwidth | 0.9 | 0.88 (slow) | 1.04 | 1.29 (fast) | GHz | FAIL | ||

| DC simulation | ||||||||

| Supply DC current | 0.19 (slow) | 0.21 | 0.23 (fast) | mA | ||||

The simulation corners are defined according to table 2.

Table 2:Corner definitions

| Corner | Vcc | Temp | Ibias | MOS |

|---|---|---|---|---|

| typ | 1.8 V | 40 C | 100u | tt |

| slow | 1.7 V | 85 C | 90u | ss |

| fast | 1.9 V | -40 C | 110u | ff |

AC response of the circuit is plotted in figure 1.

Transient simulation of the input and output waveform is plotted in figure 2.

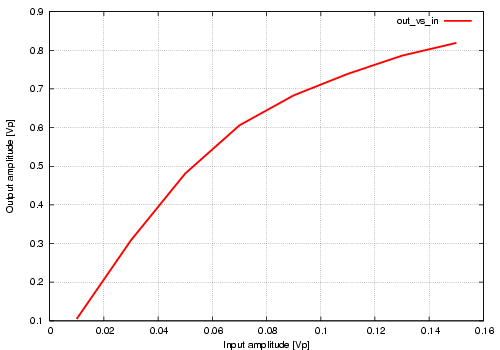

A swept simulation where the transient output amplitude vs input amplitude is plotted in figure 3.

All transient simulations are performed in the typ corner.

Fig-3: Output amplitude vs input amplitude

analysis('tran ?stop "10u" ?errpreset "moderate" )

; First run one transient simulation to store waveforms

run()

log_wave(VT("/in"), "in")

log_wave(VT("/out"), "out")

; Then sweep input amplitude and log output ampl

foreach(ampl '(10m 30m 50m 70m 90m 110m 130m 150m)

desVar("ampl" ampl)

run()

Vout_clip = clip(VT("/out"), 5u, 10u)

outampl = (ymax(Vout_clip) - ymin(Vout_clip))/2

log_data_point(ampl, outampl, "out_vs_in")

)

analysis('ac ?start "1k" ?stop "10G" )

analysis('dc ?saveOppoint t )

run()

ACgain = dB20(VF("/out"))

Gain = value(ACgain 1e7)

log_wave(ACgain, "ACgain")

log_data(Gain, "gain")

BW = cross(dB20(VF("/out")) Gain-3 1 "falling" nil nil )

log_data(BW, "BW3dB")

Idc = IDC("/V2/MINUS")

log_data(Idc, "Idc")

modelFile(

'("/afs/it.kth.se/pkg/designkits/umc/0.18/cadence/v2.6/MM-RF/TWIN_WELL/MM

/MM180_REG18_V123.lib.scs" "tt")

)

desVar( "Vsupply" 1.8 )

desVar( "Ibias" 100u )

desVar( "ampl" 0.1 )

temp( 40 )

modelFile(

'("/afs/it.kth.se/pkg/designkits/umc/0.18/cadence/v2.6/MM-RF/TWIN_WELL/MM

/MM180_REG18_V123.lib.scs" "ss")

)

desVar( "Vsupply" 1.7 )

desVar( "Ibias" 90u )

desVar( "ampl" 0.1 )

temp( 85 )

modelFile(

'("/afs/it.kth.se/pkg/designkits/umc/0.18/cadence/v2.6/MM-RF/TWIN_WELL/MM

/MM180_REG18_V123.lib.scs" "ff")

)

desVar( "Vsupply" 1.9 )

desVar( "Ibias" 110u )

desVar( "ampl" 0.1 )

temp( -40 )

Schematics:

example1 (pd_examples)