KUNGL

TEKNISKA

HÖGSKOLAN

# International Master Program in System-on-Chip Design

## L5: Boolean Circuits

### Boolean circuits

- Used for two main purposes

- as representation for Boolean functions

- as target structure for logic implementation which gets restructured in a series of logic synthesis steps until result is acceptable

- Efficient representation for most Boolean problems we have in CAD

- memory complexity is same as the size of circuits we are actually building

- Close to input representation and output representation in logic synthesis

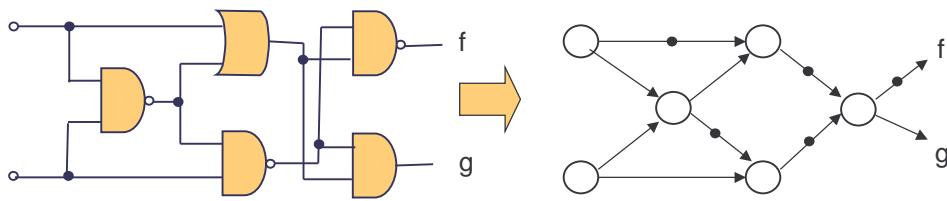

## AND-INVERTER circuits

- Base data structure uses two-input AND function for vertices and INVERTER attributes at the edges (individual bit)

- use De'Morgan's law to convert OR operation etc.

- Hash table to identify and reuse structurally isomorphic circuits (similar to BDD hash tables)

p. 3 - Advanced Logic Design – L5 - Elena Dubrova

## Notation

- $C = (V, E, \text{root})$  is a single-output directed acyclic circuit graph

- $V$  is a set of gates and primary inputs

- $E \subseteq V \times V$  is the set of edges, describing the nets connecting the gates

- $\text{root} \in V$  is the circuit output

p. 4 - Advanced Logic Design – L5 - Elena Dubrova

## Dominators in circuits

- Dominators provide a general mechanism to deal with re-converging paths in circuits

- They give the precise starting and ending points of the path

- This can be used for scheduling the creation and elimination of auxiliary variables in many applications

- Signal probability computation

- Average switching activity computation

- Equivalence and property checking (cut-points)

- Multiple-vertex dominators allow us to utilize this concept in a more practical way because they occur more frequently

---

p. 5 - Advanced Logic Design – L5 - Elena Dubrova

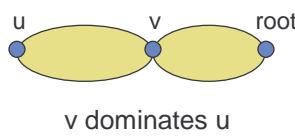

## Single-vertex dominators

- A vertex  $v$  **dominates** another vertex  $u$  if every path from  $u$  to the root contains  $v$

---

p. 6 - Advanced Logic Design – L5 - Elena Dubrova

## Immediate dominators

- Vertex  $v$  is the **immediate dominator** of  $u$ , denoted by  $v = \text{idom}(u)$ , if  $v$  dominates  $u$  and every other dominator of  $u$  dominates  $v$

- Every vertex  $v \in V$  except root has a unique immediate dominator

- The edges between  $\text{idom}(v)$  and  $v$ , for all  $v \in V$ , form a directed tree rooted at root, called the **dominator tree  $T$  of  $C$**

---

p. 7 - Advanced Logic Design – L5 - Elena Dubrova

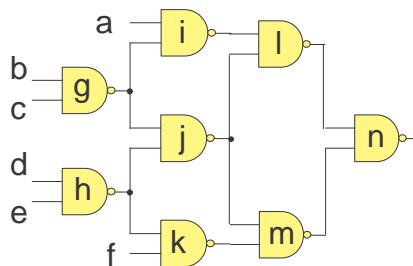

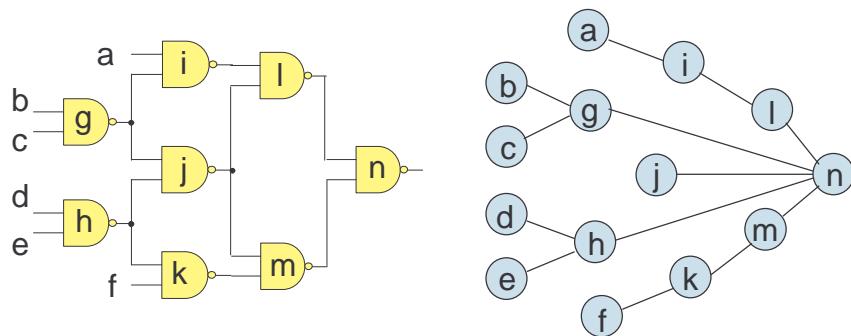

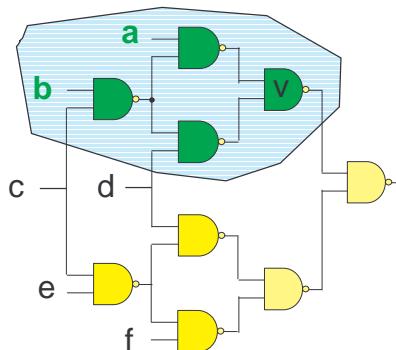

## Dominator tree example

---

p. 8 - Advanced Logic Design – L5 - Elena Dubrova

## Computing single-vertex dominators

- Efficient  $O(|V| \log|V|)$  algorithm for constructing the **dominator tree** exists (Lengauer and Tarjan, 1979)

- Single-vertex dominators are generally too rare in circuits

- Usually, there are significantly more double- and triple-vertex dominators

p. 9 - Advanced Logic Design – L5 - Elena Dubrova

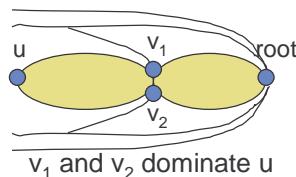

## Multiple-vertex dominators

- A set of vertices  $D = \{v_1, \dots, v_k\}$  is a multiple-vertex dominator for a vertex  $u$ , if:

1. every path from  $u$  to the root contains some  $v_i \in D$

2. for every  $v_i \in D$  there exist at least one path from  $u$  to the root which contains  $v_i \in D$  and does not contain any other  $v_j \in D$

p. 10 - Advanced Logic Design – L5 - Elena Dubrova

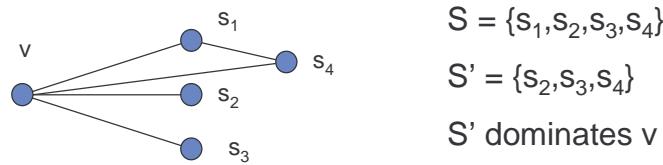

## Properties of dominators

**Property:** If  $S$  is the set of successors of  $v$ , then there exist  $S' \subseteq S$  which dominates  $v$

---

p. 11 - Advanced Logic Design – L5 - Elena Dubrova

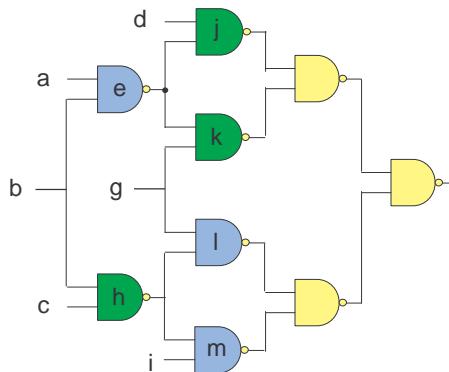

## Immediate k-vertex dominators

- The set  $D_I$  is the **immediate k-vertex dominator** of  $u$ , if  $D_I$  dominates  $u$  and there is no other  $k$ -vertex dominator  $D$  of  $u$  such that every vertex of  $D$  is dominated by  $D_I$

- For  $k > 2$ , immediate  $k$ -vertex dominators may not be unique

- No unique dominator tree exists

---

p. 12 - Advanced Logic Design – L5 - Elena Dubrova

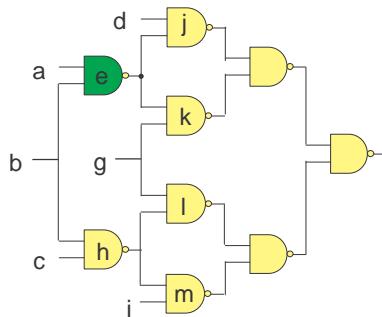

## Example

Vertex b has two immediate 3-vertex dominators: **{e,l,m}** and **{h,j,k}**

For  $k = 2$ , immediate dominators are unique

p. 13 - Advanced Logic Design – L5 - Elena Dubrova

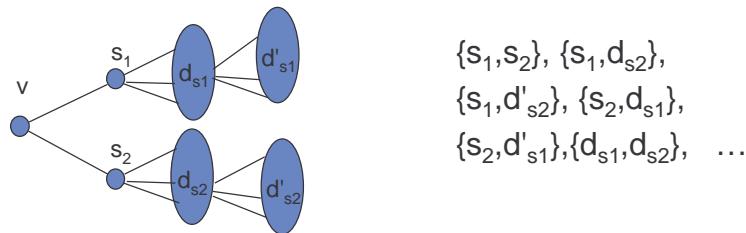

## Algorithm 1 of computing all multiple-vertex dominators

- Candidate set of the multiple-vertex dominators of  $v$  is contained in the Cartesian product

$$D_v \subseteq \{\{s_1\}, \{D_{s1}\}\} \times \{\{s_2\}, \{D_{s2}\}\} \times \dots \times \{\{s_r\}, \{D_{sr}\}\}$$

where  $\{s_1, s_2, \dots, s_r\}$  is the set of successors of  $v$

p. 14 - Advanced Logic Design – L5 - Elena Dubrova

## Alternative approach

- Large size dominators are not useful generally

- $2^k$  choices need to be examined for a  $k$ -vertex dominators

- $k = 2$  and  $k = 3$  are mostly interesting

- It is possible to efficiently compute dominators of a fixed small size  $k$

- **Basic idea:** Reduce the problem of computing the dominators of size  $k$  to the problem of computing the dominators of size  $k-1$

---

p. 15 - Advanced Logic Design – L5 - Elena Dubrova

## Dominated vertices

- Let  $\text{Dom}(v)$  be a set of vertices dominated by  $v$

- $v$  belongs to  $\text{Dom}(v)$

---

p. 16 - Advanced Logic Design – L5 - Elena Dubrova

## Algorithm II for computing all dominators of size k

For all vertices  $v \in V$ :

1. Reduce the circuit graph  $C = (V, E, \text{root})$  with respect to  $v$  by removing from  $V$  all vertices dominated by  $v$ :

$$V' = V - \text{Dom}(v)$$

$$E' = E - \{(u, w) \mid u \in \text{Dom}(v) \vee w \in \text{Dom}(v)\}$$

2. Compute dominators of size  $k-1$  for the resulting restricted graph  $C' = (V', E', \text{root})$

3. If  $D$  is a  $k-1$ -vertex dominator for  $u \in C'$ , then  $\{D, v\}$  is a  $k$ -vertex dominator for  $u \in C$ , provided  $D$  is not a  $k-1$ -vertex dominator for  $u \in C$

p. 17 - Advanced Logic Design – L5 - Elena Dubrova

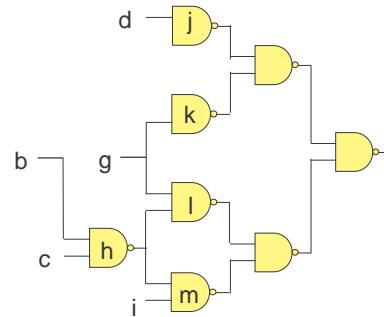

## Example

e dominates a:

- remove vertices a, e

- remove edges (a,e),(b,e),(e,g),(e,k)

h dominates b in the resulting circuit  $\Rightarrow \{h, e\}$  dominates b in the original circuit

p. 18 - Advanced Logic Design – L5 - Elena Dubrova

## Summary

- A polynomial-size algorithm for computing multiple-vertex dominators of a fixed size exists

- Useful for circuit synthesis and analysis

---

p. 19 - Advanced Logic Design – L5 - Elena Dubrova

## Open problems

- For multiple-vertex dominators, the edges  $\{(idom(v), v) \mid v \in V - \{\text{root}\}\}$  generally form an acyclic graph, rather than a tree

- How to represent the set of all possible dominators efficiently is an open problem

---

p. 20 - Advanced Logic Design – L5 - Elena Dubrova