|

|

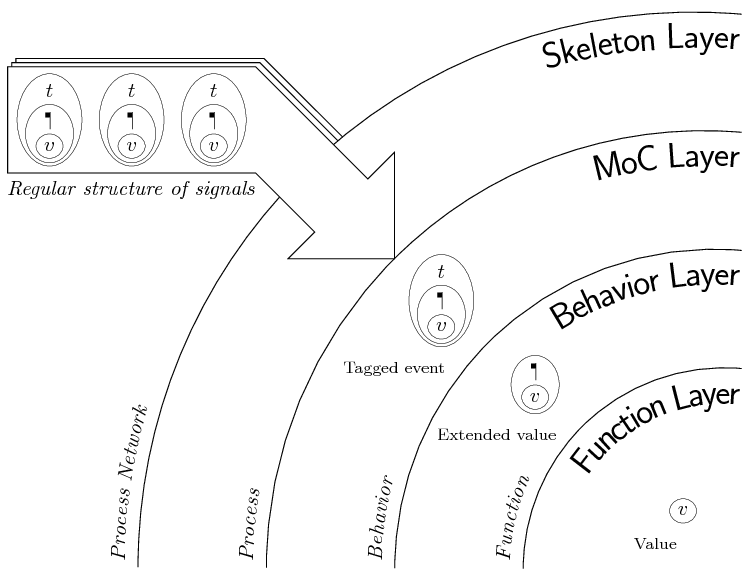

- George Ungureanu, José Edil Guimarães De Medeiros, Timmy Sundström, Ingemar Söderquist, Anders Åhlander, and Ingo Sander.

"ForSyDe-Atom: Taming Complexity in Cyber Physical System Design with Layers". in

ACM Transactions on Embedded Computing Systems (TECS), 2021, 20(2), 1-27. [

bib |

doi |

fulltext

]

- G. Ungureanu, R. Jordão and I. Sander.

"Exploiting Dataflow Models for Parallel Simulation of Discrete Timed Systems".

In 2020 Forum for Specification and Design Languages (FDL),

September 2020, (pp. 1-4). IEEE. [

fulltext |

bib |

doi

]

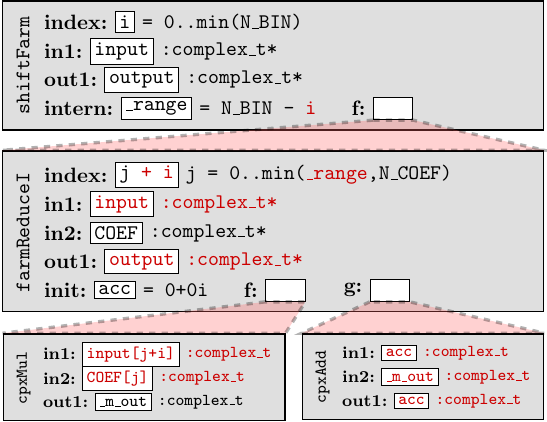

- G. Ungureanu, T. Sundström, A. Åhlander, I. Sander, and I. Söderquist.

"Formal Design, Co-Simulation and Validation of a Radar Signal Processing System".

In 2019 Forum for Specification and Design Languages (FDL),

September 2019, (pp. 1-8). IEEE. [

fulltext |

bib |

doi

]

- R. Bonna, D. S. Loubach, G. Ungureanu & I. Sander.

"Modeling and simulation of dynamic applications using scenario-aware dataflow". in

ACM Transactions on Design Automation of Electronic Systems (TODAES), 2019, 24(5), 1-29. [

bib |

doi |

url

]

- G. Ungureanu, J. E. G. de Medeiros and

I. Sander, "Bridging Discrete and Continuous

Time Models with Atoms," in Proceedings of

the 2018 Design, Automation & Test in Europe

Conference & Exhibition (DATE), 2018,

s. 277-280.[

fulltext |

bib |

urn

]

- Jose. E. G. de Medeiros, G. Ungureanu

and I. Sander, "An Algebra for Modeling

Continuous Time Systems," in Proceedings Of

the 2018 Design, Automation & Test in Europe

Conference & Exhibition (DATE), 2018,

s. 861-864.[

fulltext |

doi |

bib |

urn

]

- K. Rosvall et al., ‘Exploring Power and

Throughput for Dataflow Applications on

Predictable NoC Multiprocessors’, in 2018

21st Euromicro Conference on Digital System

Design (DSD), 2018.[

fulltext |

doi |

bib |

urn

]

- G. Ungureanu and I. Sander, ‘A layered

formal framework for modeling of

cyber-physical systems’, in Proceedings

of the 2017 Design, Automation and Test in

Europe, DATE 2017, Lausanne, Switzerland, March 2017, pp. 1715–1720.[

fulltext |

slides |

doi |

bib |

urn

]

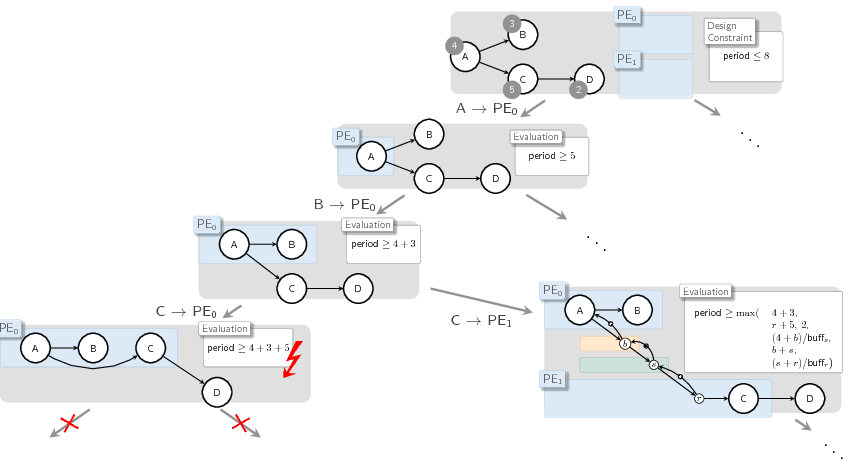

- K. Rosvall, N. Khalilzad, G. Ungureanu,

and I. Sander, ‘Throughput propagation in

constraint-based design space exploration for

mixed-criticality systems’, in Proceedings

of the 2017 Workshop on Rapid Simulation and

Performance Evaluation: Methods and Tools,

RAPIDO '17, Stockholm, Sweden. ACM,

January 2017.[

doi |

bib

]

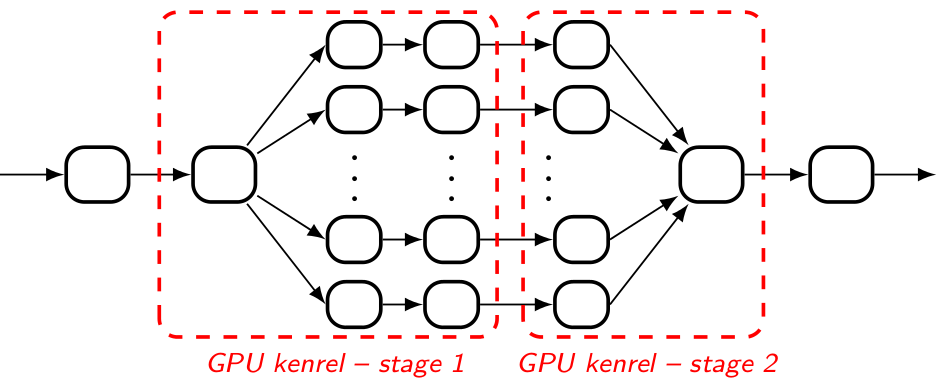

- G. Ungureanu, I. Reinhold, I. Sander, and

W. Zapka, ‘Parallel software design enabling

high-speed reliability testing of inkjet

printheads’, in Non-Impact Printing &

Digital Fabrication Conference, NIP/DF '13,

Seattle, WA, pp. 60-65, 2013. [

urn |

bib

]

|

|

|

- G. Ungureanu, T. Sundström, A. Åhlander, I. Sander, and I. Söderquist. "Design of Sensor Signal Processing with ForSyDe. Modeling, Validation and Synthesis", Technical Report 2019, KTH Royal Institute of Technology [

doi |

fulltext

]

- G. Ungureanu, "ForSyDe-Atom: User Manual", Technical Report 2018, KTH Royal Institute of Technology [

fulltext

]

- G. Ungureanu, ‘Automatic software

synthesis from high-level ForSyDe models

targeting massively parallel

processors’, Master's Thesis, KTH,

School of Information and Communication

Technology (ICT), 2013.[

urn |

bib

]

|